RL78/G1A CHAPTER 11 A/D CONVERTER

R01UH0305EJ0200 Rev.2.00 389

Jul 04, 2013

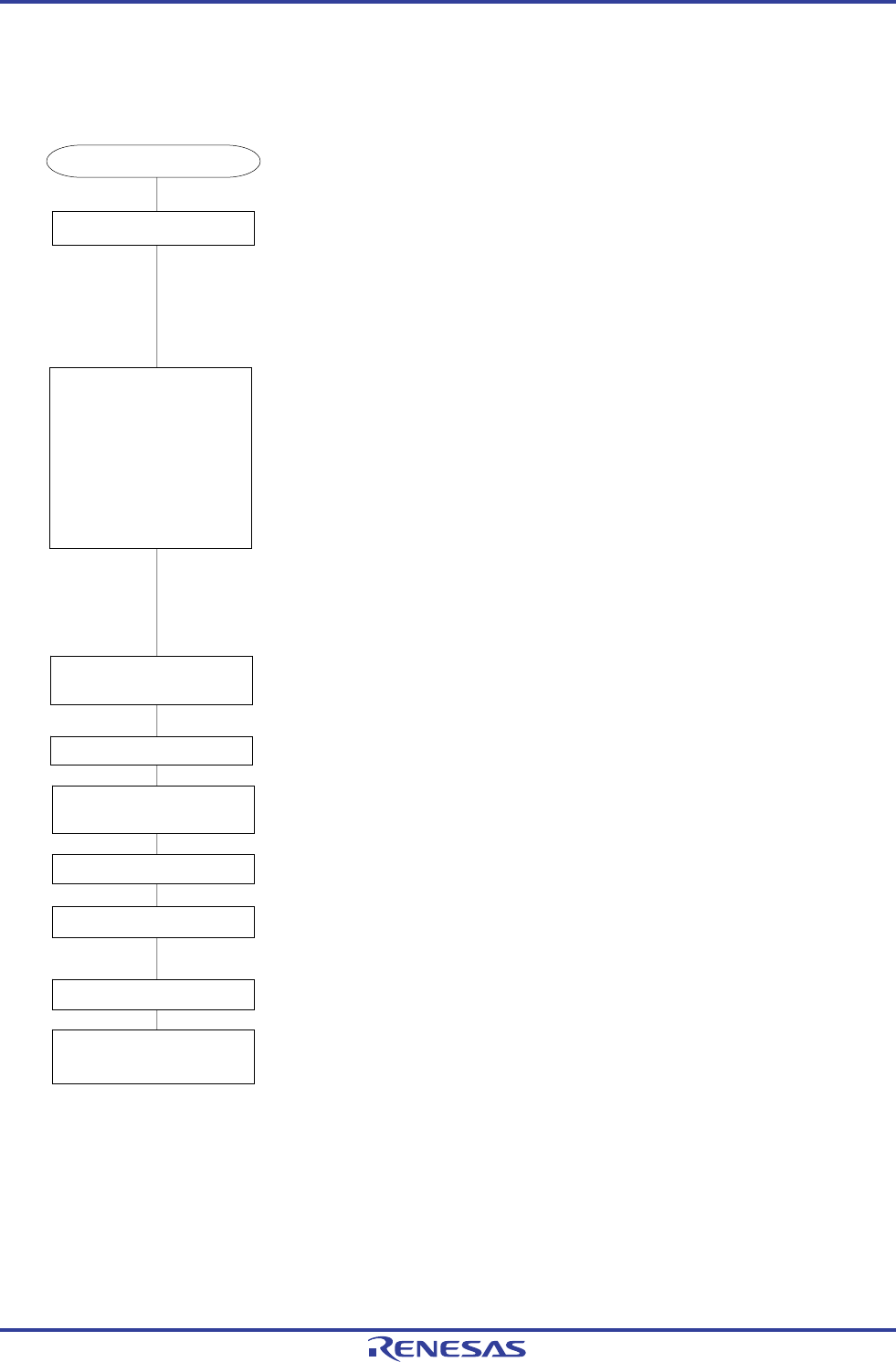

11.7.5 Setting up test mode

Figure 11-33. Setting up Test Mode

The ADCEN bit of the PER0 register is set (1), and supplying the clock starts.

• ADM0 register

FR2 to FR0, LV1, and LV0 bits: These are used to specify the A/D conversion time.

ADMD bit: This is used to specify the select mode.

• ADM1 register

ADTMD1 and ADTMD0 bits: These are used to specify the software trigger mode.

ADSCM bit: This is used to specify the one-shot conversion mode.

• ADM2 register

ADREFP1, ADREFP0, and ADREFM bits: These are used to select for the reference

voltage.

ADRCK bit: This is used to set the range for the A/D conversion result comparison

value generated by the interrupt signal to AREA2.

ADTYP bit: This is used to specify 12-bit resolution.

• ADUL/ADLL register

These set ADUL to FFH and ADLL to 00H (initial values).

• ADS register

ADS4 to ADS0 bits: These are used to set to ANI0.

The A/D conversion operations are performed.

The A/D conversion end interrupt request signal (INTAD) is generated.

Note

The conversion results are stored in the ADCR and ADCRH registers.

PER0 register setting

• ADM0 register setting

• ADM1 register setting

• ADM2 register setting

• ADUL/ADLL register setting

• ADS register setting

• ADTES register setting

(The order of the settings is

irrelevant.)

If a test mode is selected (ADTES1 bit of ADTES register = 1) as the analog input

channel: B = 0.5

μ

s

Reference voltage stabilization

wait time count B

Start of A/D conversion

End of A/D conversion

Storage of conversion results in

the ADCR and ADCRH registers

The ADCE bit of the ADM0 register is set (1), and the system enters the A/D

conversion standby status.

ADCE bit setting

ADCS bit setting

After completion of the reference voltage stabilization wait time count B, the ADCS bit

of the ADM0 register is set (1), and A/D conversion starts.

• ADTES register

ADTES1, ADTES0 bits: - side reference voltage/+ side reference voltage

Start of setup

Reference voltage stabilization

wait time count A

The reference voltage stabilization wait time count A is required when the value of the

ADREFP1 and ADREFP0 bits is changed.

If change the ADREFP1 and ADREFP0 = 1, 0: A = 10

μ

s

If change the ADREFP1 and ADREFP0 = 0, 0 or 0, 1: A = 1

μ

s

Note Depending on the settings of the ADRCK bit and ADUL/ADLL register, there is a possibility of no A/D conversion

end interrupt request signal (INTAD) being generated. In this case, the results are not stored in the ADCR,

ADCRH registers.

Caution For the procedure for testing the A/D converter, see 22.3.8 A/D test function.

<R>

<R>