RL78/G1A CHAPTER 6 TIMER ARRAY UNIT

R01UH0305EJ0200 Rev.2.00 254

Jul 04, 2013

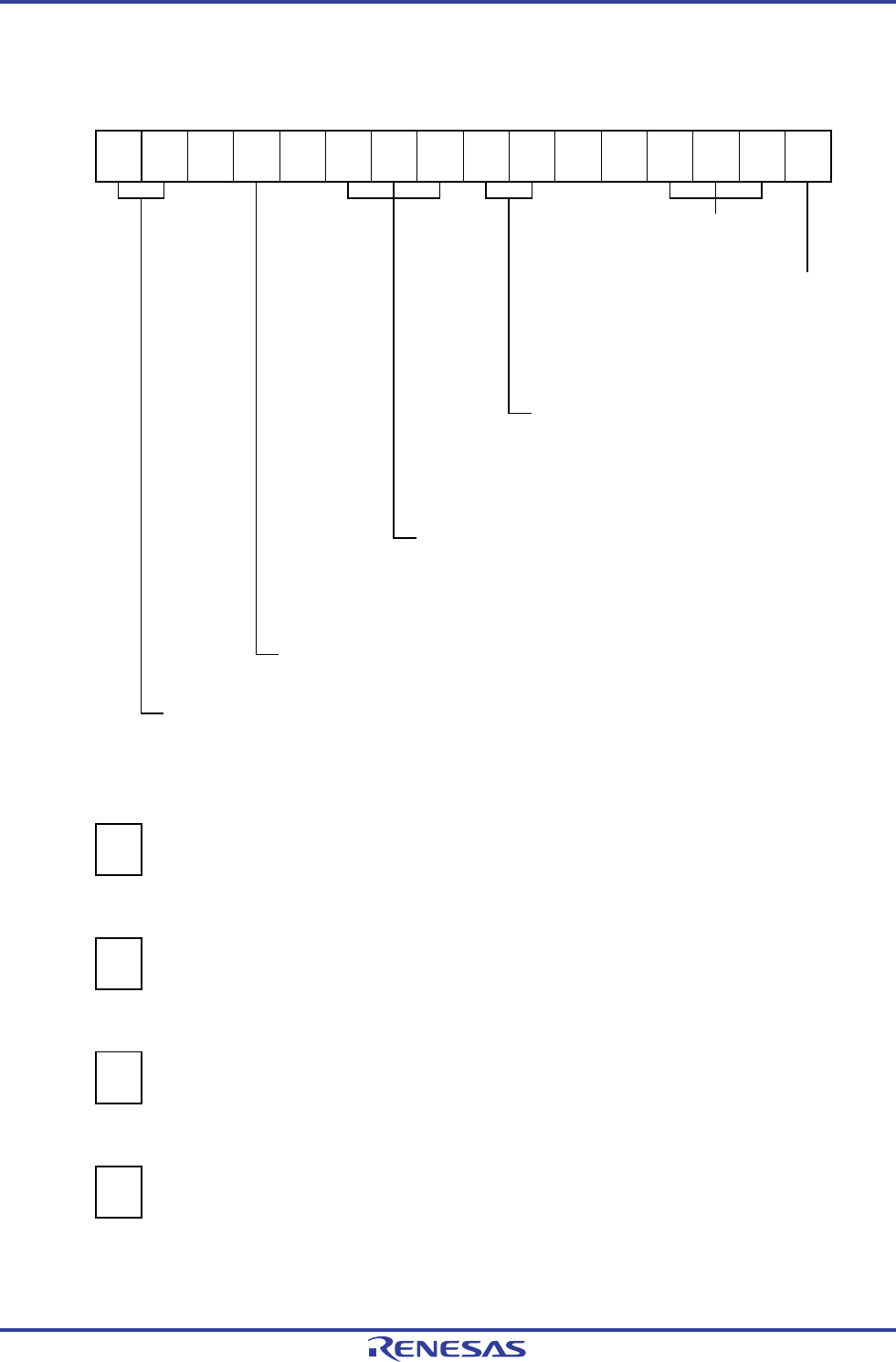

Figure 6-51. Example of Set Contents of Registers During Operation as Frequency Divider

(a) Timer mode register 00 (TMR00)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TMR00

CKS0n1

1/0

CKS0n0

0

0

CCS00

1

0

STS002

0

STS001

0

STS000

0

CIS001

1/0

CIS000

1/0

0

0

MD003

0

MD002

0

MD001

0

MD000

1/0

Operation mode of channel 0

000B: Interval timer

Setting of operation when counting is started

0: Neither generates INTTM00 nor inverts

timer output when counting is started.

1: Generates INTTM00 and inverts timer

output when counting is started.

Selection of TI00 pin input edge

00B: Detects falling edge.

01B: Detects rising edge.

10B: Detects both edges.

11B: Setting prohibited

Start trigger selection

000B: Selects only software start.

Count clock selection

1: Selects the TI00 pin input valid edge.

Operation clock (f

MCK) selection

00B: Selects CK00 as operation clock of channel 0.

10B: Selects CK01 as operation clock of channel 0.

(b) Timer output register 0 (TO0)

Bit 0

TO0

TO00

1/0

0: Outputs 0 from TO00.

1: Outputs 1 from TO00.

(c) Timer output enable register 0 (TOE0)

Bit 0

TOE0

TOE00

1/0

0: Stops the TO00 output operation by counting operation.

1: Enables the TO00 output operation by counting operation.

(d) Timer output level register 0 (TOL0)

Bit 0

TOL0

TOL00

0

0: Cleared to 0 when TOM00 = 0 (master channel output mode)

(e) Timer output mode register 0 (TOM0)

Bit 0

TOM0

TOM00

0

0: Sets master channel output mode.

<R>