RL78/G1A CHAPTER 15 DMA CONTROLLER

(4) DMA pending instruction

Even if a DMA request is generated, DMA transfer is held pending immediately after the following instructions.

• CALL !addr16

<R>

• CALL $!addr20

• CALL !!addr20

• CALL rp

• CALLT [addr5]

• BRK

• MOV PSW, #byte

• MOV PSW, A

• MOV1 PSW. bit, CY

• SET1 PSW. bit

• CLR1 PSW. bit

• POP PSW

• BTCLR PSW. bit, $addr20

• EI

• DI

• Write instructions for registers IF0L, IF0H, IF1L, IF1H, IF2L, IF2H, MK0L, MK0H, MK1L, MK1H, MK2L, MK2H,

PR00L, PR00H, PR01L, PR01H, PR02L, PR02H, PR10L, PR10H, PR11L, PR11H, PR12L, and PR12H each.

• Instruction for accessing the data flash memory

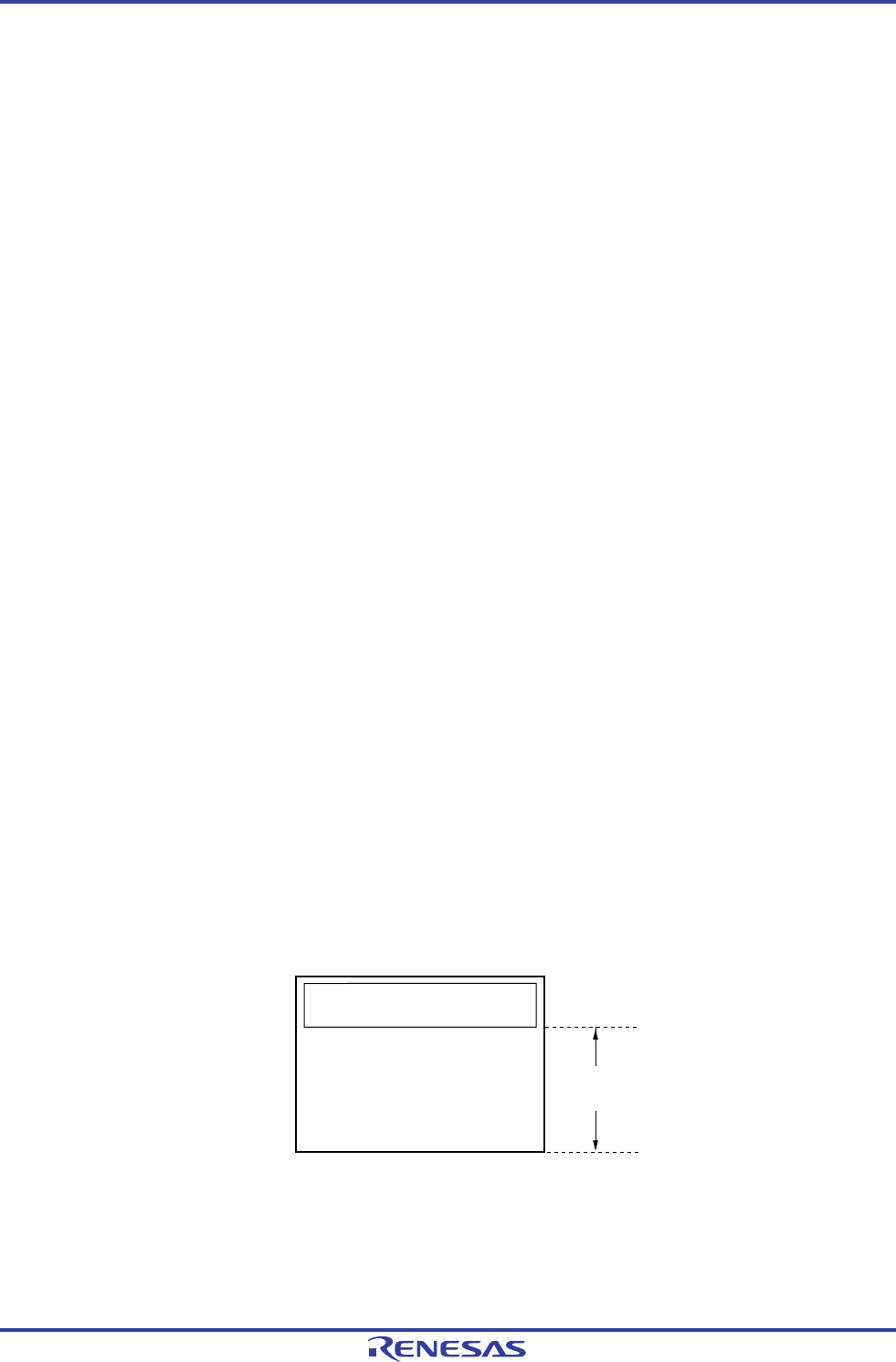

(5) Operation if address in general-purpose register area or other than those of internal RAM area is specified

The address indicated by DMA RAM address register n (DRAn) is incremented during DMA transfer. If the

address is incremented to an address in the general-purpose register area or exceeds the area of the internal RAM,

the following operation is performed.

z In mode of transfer from SFR to RAM

The data of that address is lost.

z In mode of transfer from RAM to SFR

Undefined data is transferred to SFR.

In either case, malfunctioning may occur or damage may be done to the system. Therefore, make sure that the

address is within the internal RAM area other than the general-purpose register area.

Internal RAM

General-purpose registers

DMA transfer enabled area

FFF00H

FFEFFH

FFEE0H

FFEDFH

R01UH0305EJ0200 Rev.2.00 686

Jul 04, 2013