RL78/G1A CHAPTER 12 SERIAL ARRAY UNIT

R01UH0305EJ0200 Rev.2.00 411

Jul 04, 2013

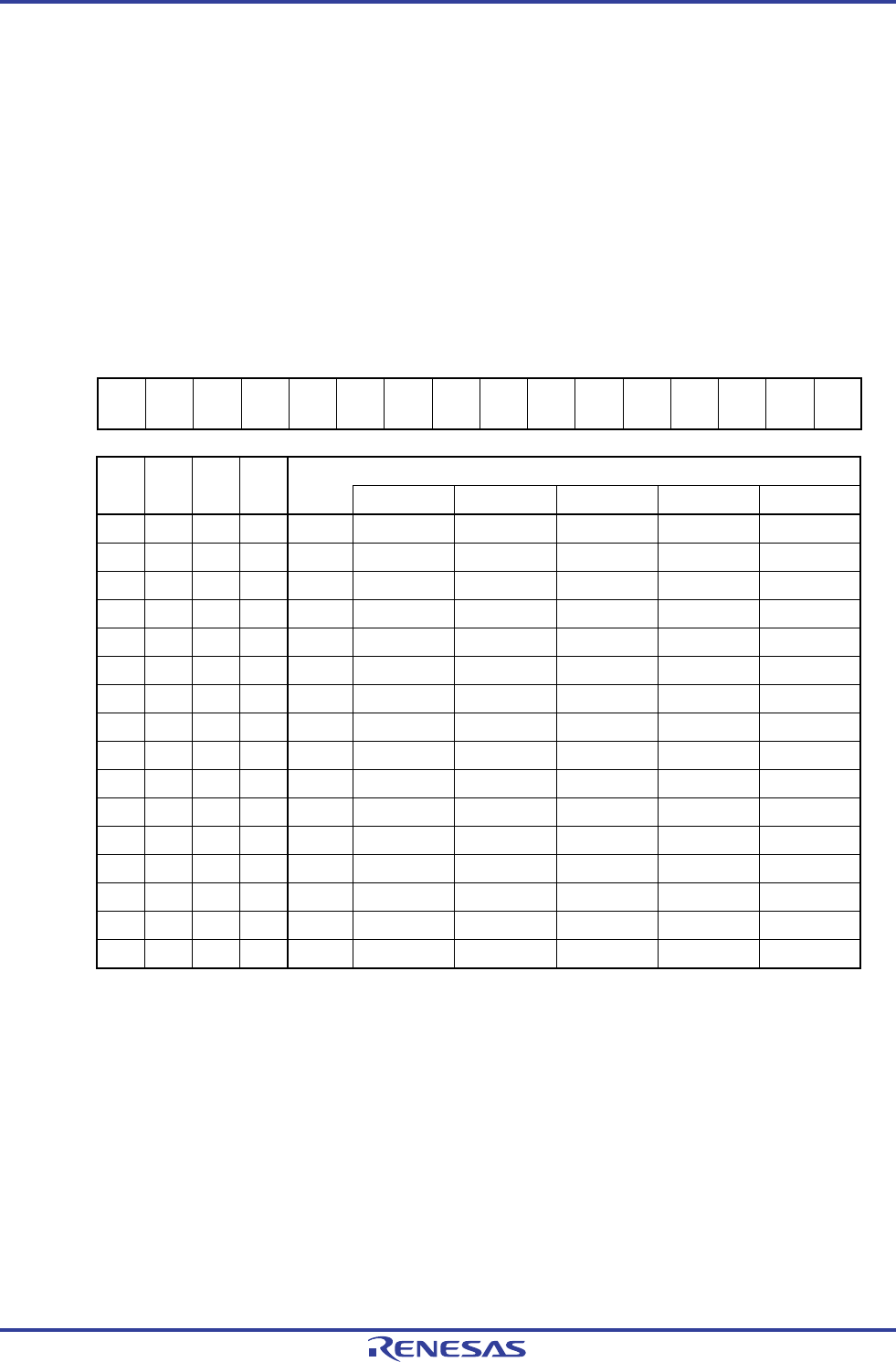

12.3.2 Serial clock select register m (SPSm)

The SPSm register is a 16-bit register that is used to select two types of operation clocks (CKm0, CKm1) that are

commonly supplied to each channel. CKm1 is selected by bits 7 to 4 of the SPSm register, and CKm0 is selected by bits

3 to 0.

Rewriting the SPSm register is prohibited when the register is in operation (when SEmn = 1).

The SPSm register can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of the SPSm register can be set with an 8-bit memory manipulation instruction with SPSmL.

Reset signal generation clears the SPSm register to 0000H.

Figure 12-5. Format of Serial Clock Select Register m (SPSm)

Address: F0126H, F0127H (SPS0), F0166H, F0167H (SPS1)

Note 1

After reset: 0000H R/W

Symbol 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SPSm 0 0 0 0 0 0 0 0

PRS

m13

PRS

m12

PRS

m11

PRS

m10

PRS

m03

PRS

m02

PRS

m01

PRS

m00

Section of operation clock (CKmk)

Note 2

PRS

mk3

PRS

mk2

PRS

mk1

PRS

mk0

f

CLK = 2 MHz fCLK = 5 MHz fCLK = 10 MHz fCLK = 20 MHz fCLK = 32 MHz

0 0 0 0 fCLK 2 MHz 5 MHz 10 MHz 20 MHz 32 MHz

0 0 0 1 fCLK/2 1 MHz 2.5 MHz 5 MHz 10 MHz 16 MHz

0 0 1 0 fCLK/2

2

500 kHz 1.25 MHz 2.5 MHz 5 MHz 8 MHz

0 0 1 1 fCLK/2

3

250 kHz 625 kHz 1.25 MHz 2.5 MHz 4 MHz

0 1 0 0 fCLK/2

4

125 kHz 313 kHz 625 kHz 1.25 MHz 2 MHz

0 1 0 1 fCLK/2

5

62.5 kHz 156 kHz 313 kHz 625 kHz 1 MHz

0 1 1 0 fCLK/2

6

31.3 kHz 78.1 kHz 156 kHz 313 kHz 500 kHz

0 1 1 1 fCLK/2

7

15.6 kHz 39.1 kHz 78.1 kHz 156 kHz 250 kHz

1 0 0 0 fCLK/2

8

7.81 kHz 19.5 kHz 39.1 kHz 78.1 kHz 125 kHz

1 0 0 1 fCLK/2

9

3.91 kHz 9.77 kHz 19.5 kHz 39.1 kHz 62.5 kHz

1 0 1 0 fCLK/2

10

1.95 kHz 4.88 kHz 9.77 kHz 19.5 kHz 31.3 kHz

1 0 1 1 fCLK/2

11

977 Hz 2.44 kHz 4.88 kHz 9.77 kHz 15.6 kHz

1 1 0 0 fCLK/2

12

488 Hz 1.22 kHz 2.44 kHz 4.88 kHz 7.81 kHz

1 1 0 1 fCLK/2

13

244 Hz 610 Hz 1.22 kHz 2.44 kHz 3.91 kHz

1 1 1 0 fCLK/2

14

122 Hz 305 Hz 610 Hz 1.22 kHz 1.95 kHz

1 1 1 1 fCLK/2

15

61 Hz 153 kHz 305 Hz 610 Hz 977 Hz

Notes 1. 32, 48, and 64-pin products

2. When changing the clock selected for f

CLK (by changing the system clock control register (CKC) value),

do so after having stopped (serial channel stop register m (STm) = 000FH) the operation of the serial

array unit (SAU).

Caution Be sure to clear bits 15 to 8 to “0”.

Remarks 1. f

CLK: CPU/peripheral hardware clock frequency

2. m: Unit number (m = 0, 1)

3. k = 0, 1

<R>