RL78/G1A CHAPTER 5 CLOCK GENERATOR

R01UH0305EJ0200 Rev.2.00 174

Jul 04, 2013

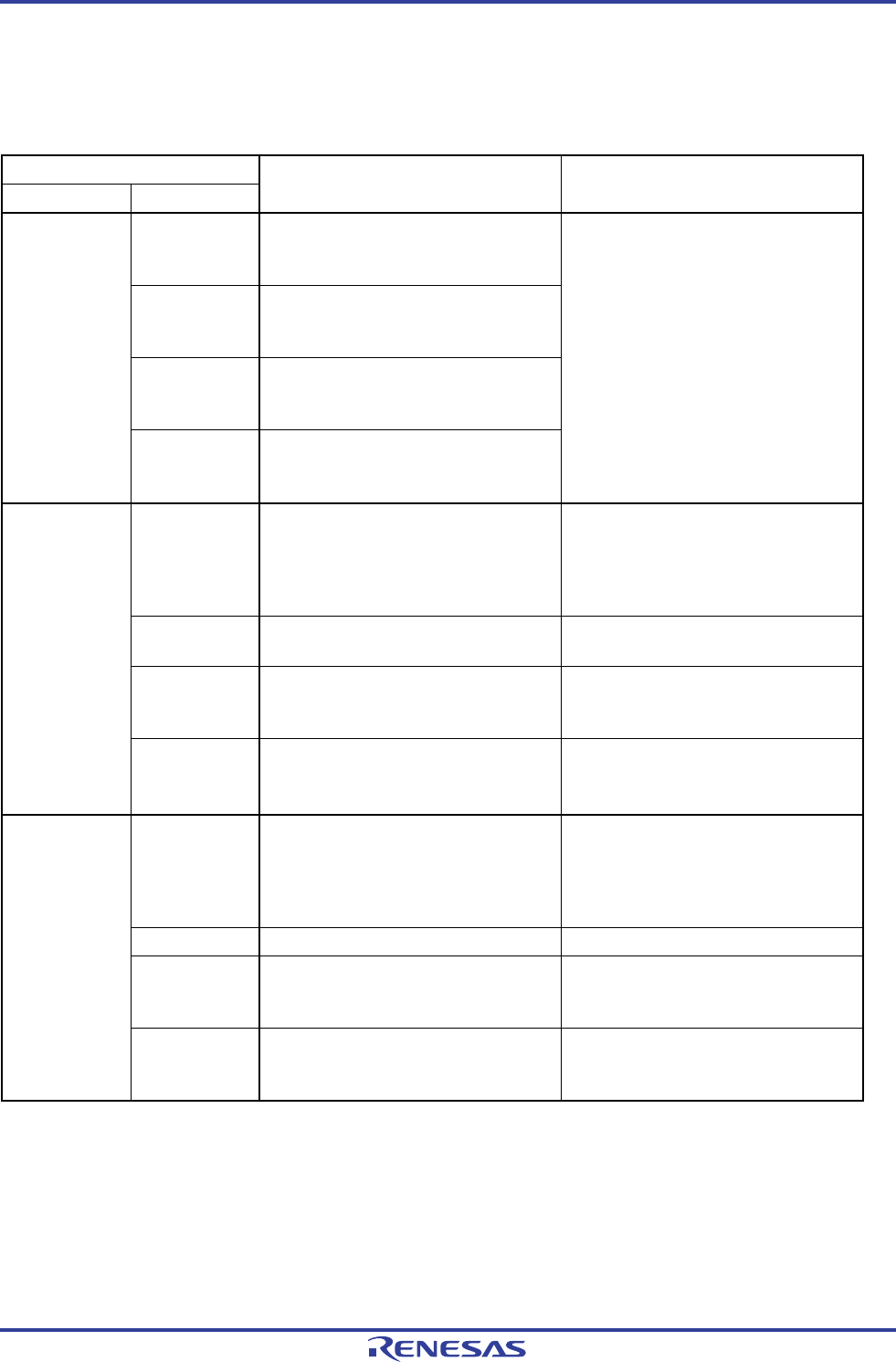

5.6.5 Condition before changing CPU clock and processing after changing CPU clock

Condition before changing the CPU clock and processing after changing the CPU clock are shown below.

Table 5-4. Changing CPU Clock (1/2)

CPU Clock

Before Change After Change

Condition Before Change Processing After Change

X1 clock

Stabilization of X1 oscillation

• OSCSEL = 1, EXCLK = 0, MSTOP = 0

• After elapse of oscillation stabilization time

External main

system clock

Enabling input of external clock from the

EXCLK pin

• OSCSEL = 1, EXCLK = 1, MSTOP = 0

XT1 clock

Stabilization of XT1 oscillation

• OSCSELS = 1, EXCLKS = 0, XTSTOP = 0

• After elapse of oscillation stabilization time

High-speed on-

chip oscillator

clock

External

subsystem clock

Enabling input of external clock from the

EXCLKS pin

• OSCSELS = 1, EXCLKS = 1, XTSTOP = 0

Operating current can be reduced by

stopping high-speed on-chip oscillator

(HIOSTOP = 1).

High-speed on-

chip oscillator

clock

Enabling oscillation of high-speed on-chip

oscillator

• HIOSTOP = 0

• After elapse of oscillation accuracy

stabilization time

X1 oscillation can be stopped (MSTOP = 1).

External main

system clock

Transition not possible

−

XT1 clock

Stabilization of XT1 oscillation

• OSCSELS = 1, EXCLKS = 0, XTSTOP = 0

• After elapse of oscillation stabilization time

X1 oscillation can be stopped (MSTOP = 1).

X1 clock

External

subsystem clock

Enabling input of external clock from the

EXCLKS pin

• OSCSELS = 1, EXCLKS = 1, XTSTOP = 0

X1 oscillation can be stopped (MSTOP = 1).

High-speed on-

chip oscillator

clock

Enabling oscillation of high-speed on-chip

oscillator

• HIOSTOP = 0

• After elapse of oscillation accuracy

stabilization time

External main system clock input can be

disabled (MSTOP = 1).

X1 clock

Transition not possible

−

XT1 clock

Stabilization of XT1 oscillation

• OSCSELS = 1, EXCLKS = 0, XTSTOP = 0

• After elapse of oscillation stabilization time

External main system clock input can be

disabled (MSTOP = 1).

External main

system clock

External

subsystem clock

Enabling input of external clock from the

EXCLKS pin

• OSCSELS = 1, EXCLKS = 1, XTSTOP = 0

External main system clock input can be

disabled (MSTOP = 1).

<R>

<R>