RL78/G1A CHAPTER 19 RESET FUNCTION

19.2 States of Operation During Reset Periods

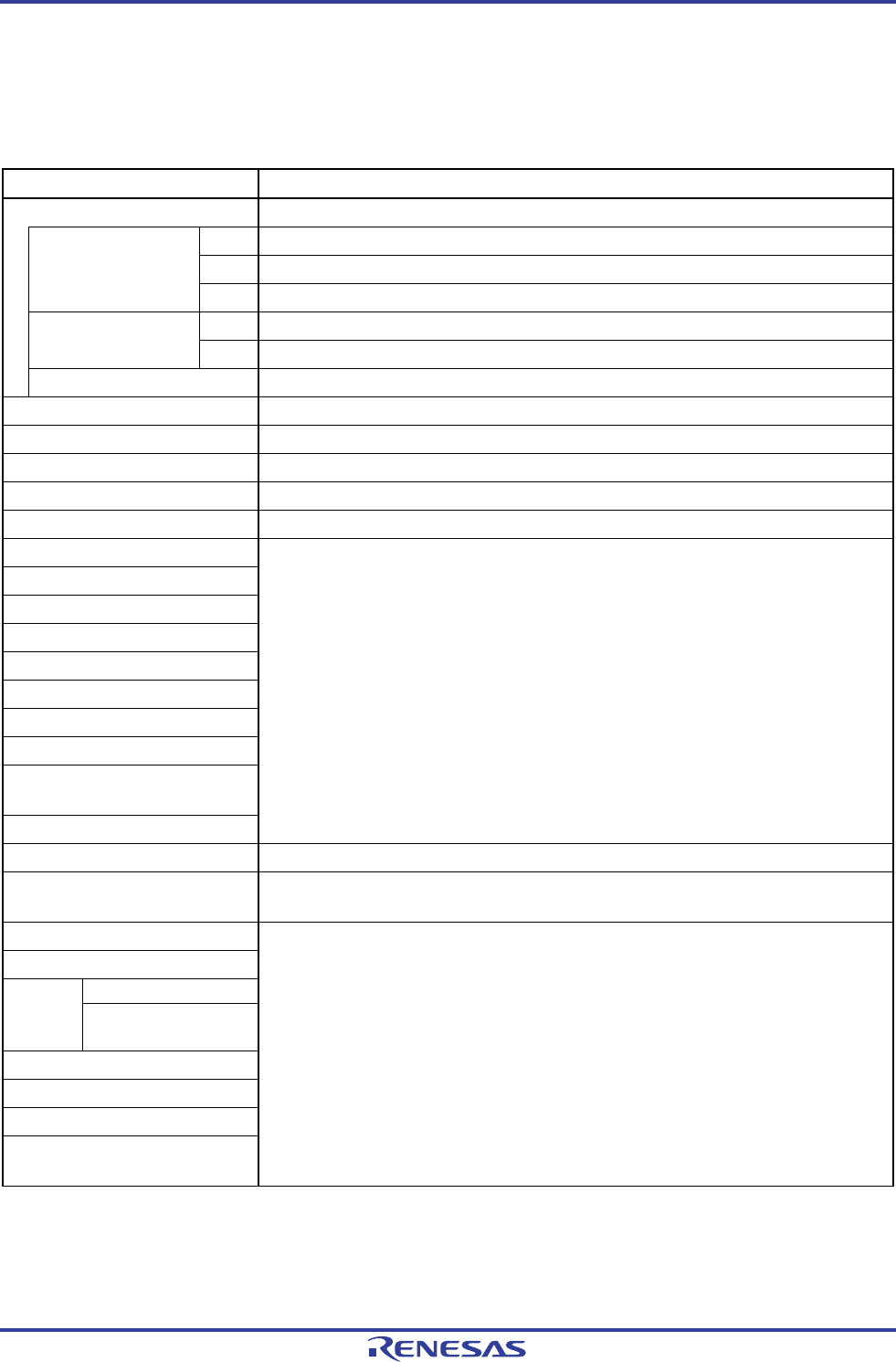

Table 19-1 shows the states of operation during reset periods. Table 19-2 shows the states of the hardware after

receiving a reset signal.

Table 19-1. States of Operation During Reset Period

Item During Reset Period

System clock Clock supply to the CPU is stopped.

fIH Operation stopped

fX Operation stopped (the X1 and X2 pins are input port mode)

Main system clock

fEX Clock input invalid (the pin is input port mode)

fXT Operation stopped (the XT1 and XT2 pins are input port mode)

Subsystem clock

fEXS Clock input invalid (the pin is input port mode)

fIL Operation stopped

CPU Operation stopped

Code flash memory Operation stopped

Data flash memory Operation stopped

RAM Operation stopped

Port (latch) High impedance

Note

Timer array unit

Real-time clock (RTC)

12-bit interval timer

Watchdog timer

Clock output/buzzer output

A/D converter

Serial array unit (SAU)

Serial interface (IICA)

Multiplier & divider, multiply-

accumulator

DMA controller

Operation stopped

Power-on-reset function Detection operation possible

Voltage detection function

Operation is possible in the case of an LVD reset and stopped in the case of other types of

reset.

External interrupt

Key interrupt function

High-speed CRC

CRC

operation

function

General-purpose CRC

RAM parity error detection function

RAM guard function

SFR guard function

Illegal-memory access detection

function

Operation stopped

<R>

<R>

Note P40 and P130 become the following state.

<R>

• P40: High-impedance during the external reset period or reset period by the POR. High level during other

types of reset (connected to the internal pull-up resistor).

• P130: Low level during the reset period

(Remark is listed on the next page.)

R01UH0305EJ0200 Rev.2.00 744

Jul 04, 2013