RL78/G1A CHAPTER 12 SERIAL ARRAY UNIT

R01UH0305EJ0200 Rev.2.00 547

Jul 04, 2013

12.8.1 Address field transmission

Address field transmission is a transmission operation that first executes in I

2

C communication to identify the target for

transfer (slave). After a start condition is generated, an address (7 bits) and a transfer direction (1 bit) are transmitted in

one frame.

Simplified I

2

C

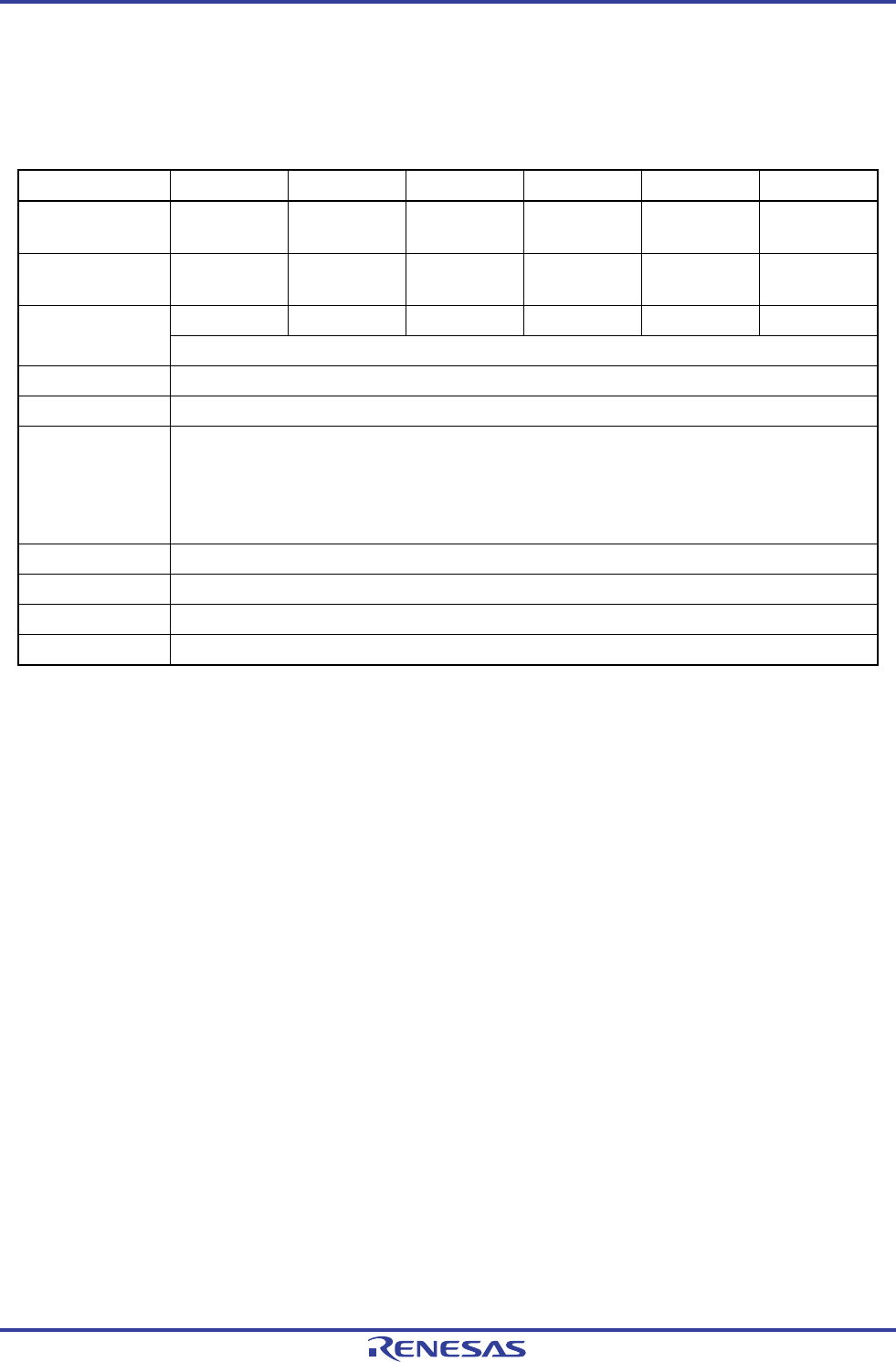

IIC00 IIC01 IIC10 IIC11 IIC20 IIC21

Target channel Channel 0 of

SAU0

Channel 1 of

SAU0

Channel 2 of

SAU0

Channel 3 of

SAU0

Channel 0 of

SAU1

Channel 1 of

SAU1

Pins used SCL00,

SDA00

Note 1

SCL01,

SDA01

Note 1

SCL10,

SDA10

Note 1

SCL11,

SDA11

Note 1

SCL20,

SDA20

Note 1

SCL21,

SDA21

Note 1

INTIIC00 INTIIC01 INTIIC10 INTIIC11 INTIIC20 INTIIC21 Interrupt

Transfer end interrupt only (Setting the buffer empty interrupt is prohibited.)

Error detection flag ACK error detection flag (PEFmn)

Transfer data length 8 bits (transmitted with specifying the higher 7 bits as address and the least significant bit as R/W control)

Transfer rate

Note 2

Max. fMCK/4 [MHz] (SDRmn[15:9] = 1 or more) fMCK: operation clock frequency of target channel

However, the following condition must be satisfied in each mode of I

2

C.

• Max. 1 MHz (first mode plus)

• Max. 400 kHz (first mode)

• Max. 100 kHz (standard mode)

Data level Non-reversed output (default: high level)

Parity bit No parity bit

Stop bit Appending 1 bit (or ACK reception timing)

Data direction MSB first

Notes 1. To perform communication via simplified I

2

C, set the N-ch open-drain output (VDD tolerance (25- to 48-pin

products/EV

DD tolerance (64-pin products)) mode (POMxx = 1) for the port output mode registers (POMxx).

See 4.3 Registers Controlling Port Function and 4.5 Register Settings When Using Alternate Function

for details.

When IIC00, IIC10, IIC20 communicating with an external device with a different potential, set the N-ch open-

drain output (V

DD tolerance (25 to 48-pin products/EVDD tolerance (64-pin products)) mode (POMxx = 1) also for

the clock input/output pins (SCL00, SCL10, SCL20). See 4.4.5 Handling different potential (1.8 V, 2.5 V) by

using I/O buffers for details.

2. Use this operation within a range that satisfies the conditions above and the peripheral functions characteristics

in the electrical specifications (see CHAPTER 29 ELECTRICAL SPECIFICATIONS (T

A = −40 to +85°C) and

CHAPTER 30 ELECTRICAL SPECIFICATIONS (G: INDUSTRIAL APPLICATIONS T

A = −40 to +105°C)).

Remark m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), mn = 00 to 03, 10, 11

<R>

<R>