RL78/G1A CHAPTER 4 PORT FUNCTIONS

R01UH0305EJ0200 Rev.2.00 109

Jul 04, 2013

4.3.5 Port output mode registers (POMxx)

These registers set the output mode in 1-bit units.

N-ch open drain output (V

DD tolerance

Note 1

/EVDD tolerance

Note 2

) mode can be selected during serial communication with

an external device of the different potential, and for the SDA00, SDA01, SDA10, SDA11, SDA20, and SDA21 pins during

simplified I

2

C communication with an external device of the same potential.

In addition, POMxx register is set with PUxx register, whether or not to use the on-chip pull-up resistor.

These registers can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears these registers to 00H.

Caution An on-chip pull-up resistor is not connected to a bit for which N-ch open drain output (V

DD

tolerance

Note 1

/EVDD tolerance

Note 2

) mode (POMmn = 1) is set.

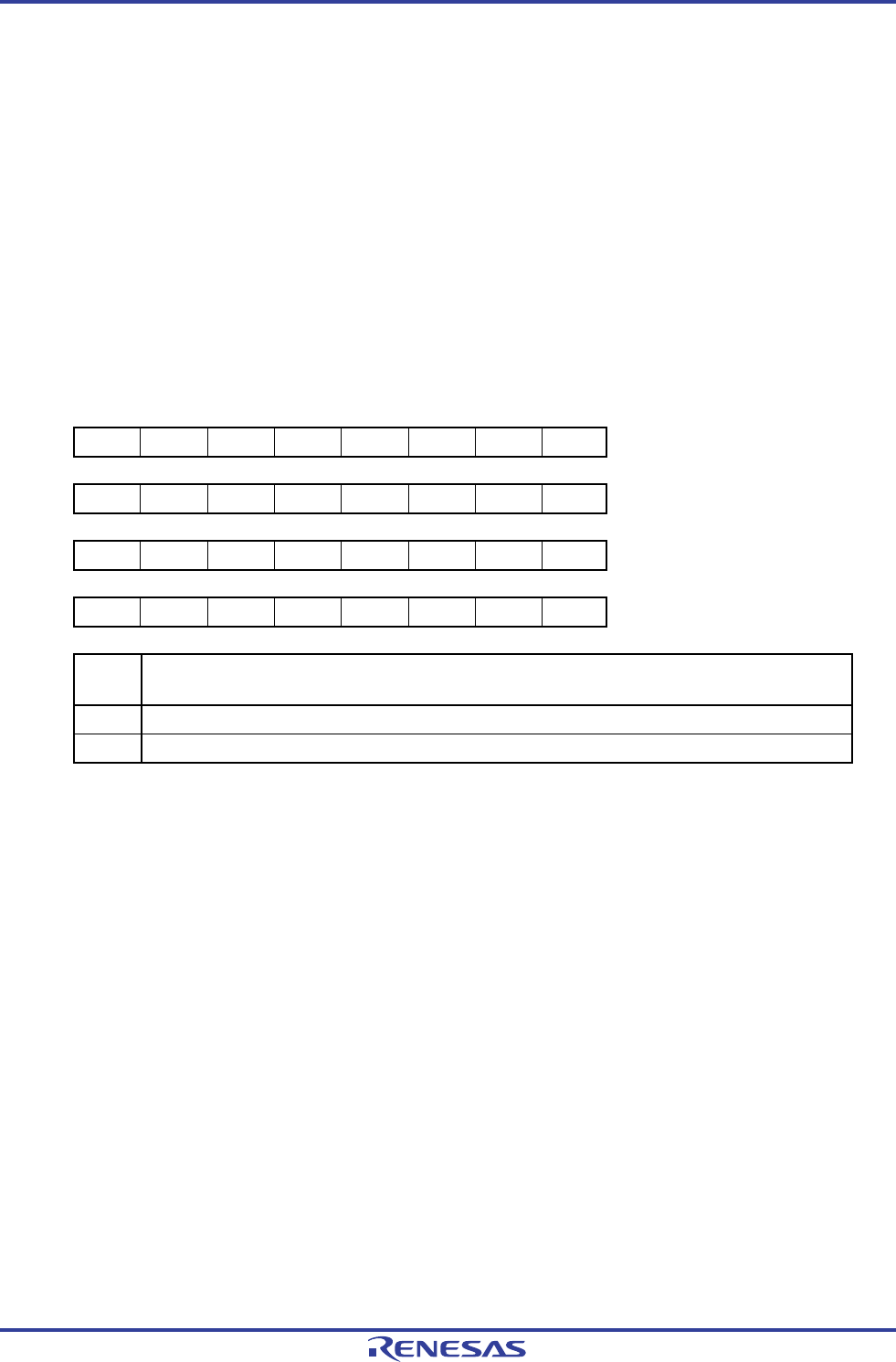

Figure 4-5. Format of Port Input Mode Register

Symbol 7 6 5 4 3 2 1 0 Address After reset R/W

POM0 0 0 0 POM04 POM03 POM02 0 0 F0050H 00H R/W

POM1 0 0 POM15 POM14 POM13 POM12 POM11 POM10 F0051H 00H R/W

POM5 0 0 0 0 0 0 0 POM50 F0055H 00H R/W

POM7 0 0 0 POM74 0 0 POM71 0 F0057H 00H R/W

POMmn

Pmn pin output mode selection

(m = 0, 1, 5, 7; n = 0 to 5)

0 Normal output mode

1 N-ch open-drain output (VDD tolerance

Note 1

/EVDD tolerance

Note 2

) mode

Notes 1. For 25- to 48-pin products

2. For 64-pin products

Caution Be sure to set bits that are not mounted to their initial values.

<R>

<R>

<R>

<R>