RL78/G1A CHAPTER 15 DMA CONTROLLER

15.5.5 Forced termination by software

After the DSTn bit is set to 0 by software, it takes up to 2 clocks until a DMA transfer is actually stopped and the DSTn

bit is set to 0. To forcibly terminate a DMA transfer by software without waiting for occurrence of the interrupt (INTDMAn)

of DMAn, therefore, perform either of the following processes.

<When using one DMA channel>

• Set the DSTn bit to 0 (use DRCn = 80H to write with an 8-bit manipulation instruction) by software, confirm by polling

that the DSTn bit has actually been cleared to 0, and then set the DENn bit to 0 (use DRCn = 00H to write with an 8-

bit manipulation instruction).

• Set the DSTn bit to 0 (use DRCn = 80H to write with an 8-bit manipulation instruction) by software and then set the

DENn bit to 0 (use DRCn = 00H to write with an 8-bit manipulation instruction) two or more clocks after.

<When using two or more DMA channels>

• To forcibly terminate DMA transfer by software when using two or more DMA channels (by setting DSTn to 0), clear

the DSTn bit to 0 after the DMA transfer is held pending by setting the DWAITn bits of all using channels to 1. Next,

clear the DWAITn bits of all using channels to 0 to cancel the pending status, and then clear the DENn bit to 0.

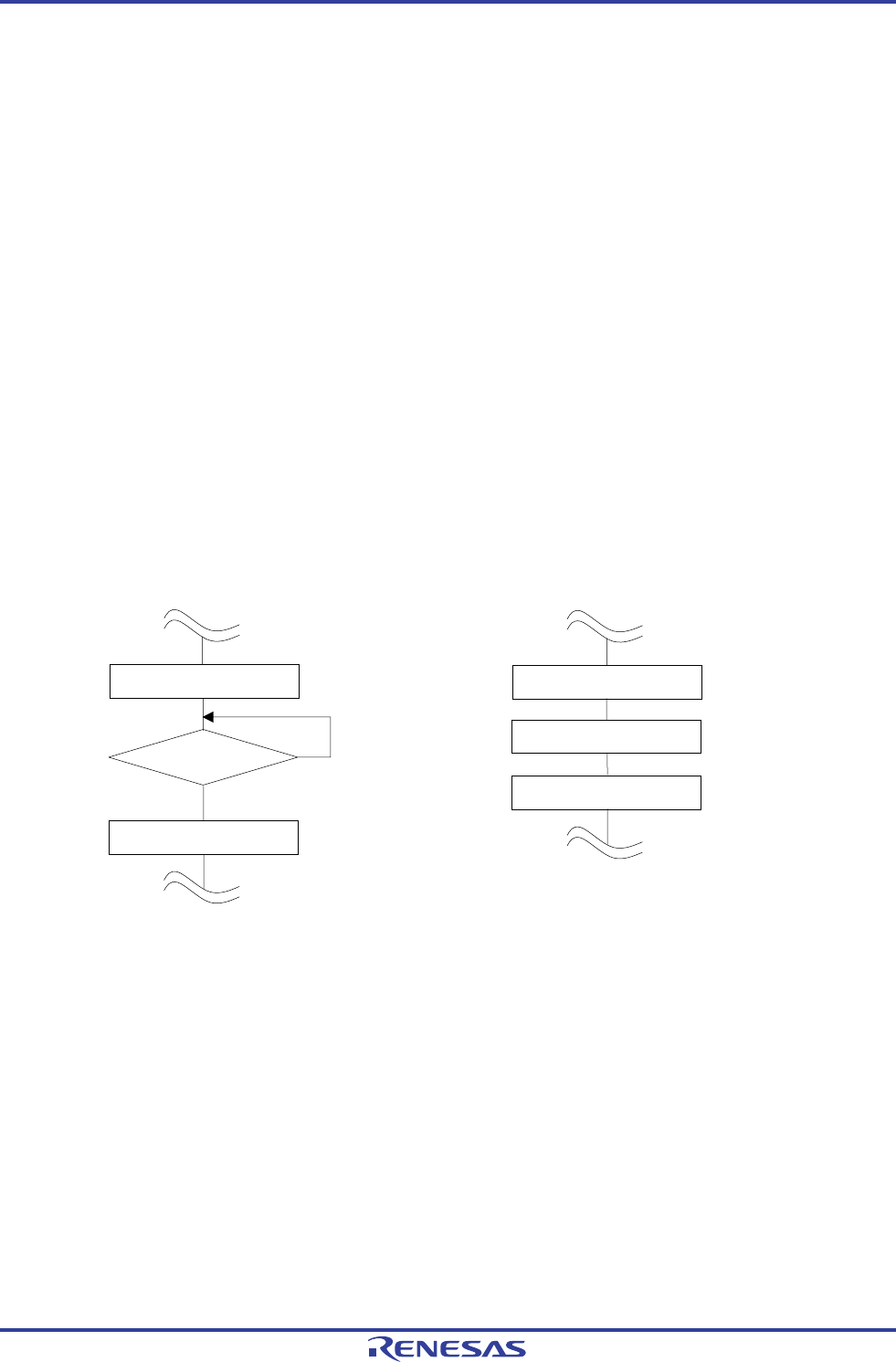

Figure 15-11. Forced Termination of DMA Transfer (1/2)

Example 1 Example 2

DSTn = 0

DENn = 0

DSTn = 0?

No

2 clock wait

Yes

DSTn = 0

DENn = 0

Remarks 1. n: DMA channel number (n = 0, 1)

2. 1 clock: 1/f

CLK (fCLK: CPU clock)

R01UH0305EJ0200 Rev.2.00 683

Jul 04, 2013