RL78/G1A CHAPTER 16 INTERRUPT FUNCTIONS

16.4 Interrupt Servicing Operations

16.4.1 Maskable interrupt request acknowledgment

A maskable interrupt request becomes acknowledgeable when the interrupt request flag is set to 1 and the mask (MK)

flag corresponding to that interrupt request is cleared to 0. A vectored interrupt request is acknowledged if interrupts are

in the interrupt enabled state (when the IE flag is set to 1). However, a low-priority interrupt request is not acknowledged

during servicing of a higher priority interrupt request.

The times from generation of a maskable interrupt request until vectored interrupt servicing is performed are listed in

Table 16-4 below.

For the interrupt request acknowledgment timing, see Figures 16-8 and 16-9.

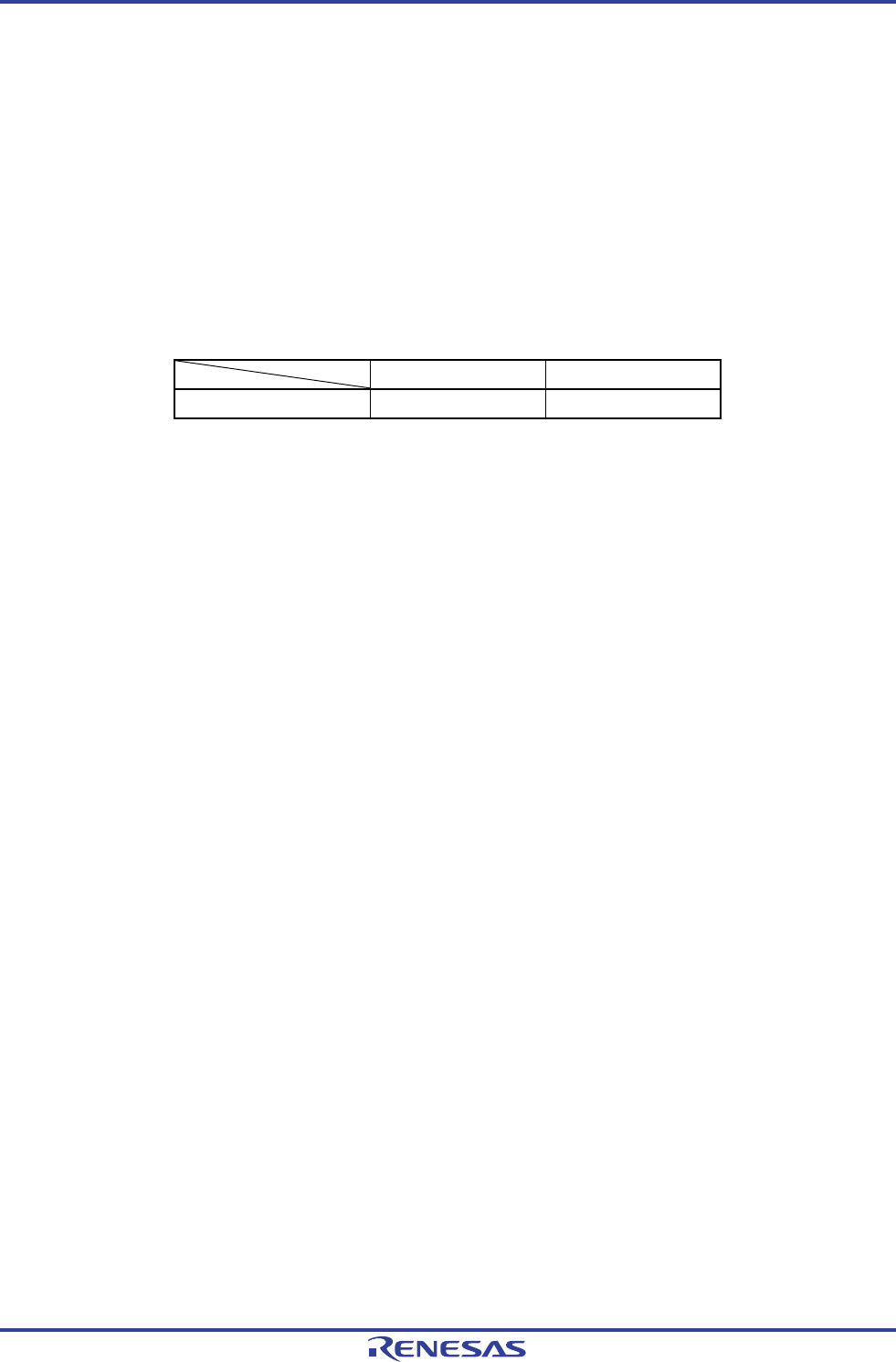

Table 16-4. Time from Generation of Maskable Interrupt Until Servicing

Minimum Time Maximum Time

Note

Servicing time 9 clocks 16 clocks

Note Maximum time does not apply when an instruction from the internal RAM area is executed.

Remark 1 clock: 1/f

CLK (fCLK: CPU clock)

If two or more maskable interrupt requests are generated simultaneously, the request with a higher priority level

specified in the priority specification flag is acknowledged first. If two or more interrupts requests have the same priority

level, the request with the highest default priority is acknowledged first.

An interrupt request that is held pending is acknowledged when it becomes acknowledgeable.

Figure 16-7 shows the interrupt request acknowledgment algorithm.

If a maskable interrupt request is acknowledged, the contents are saved into the stacks in the order of PSW, then PC,

the IE flag is reset (0), and the contents of the priority specification flag corresponding to the acknowledged interrupt are

transferred to the ISP1 and ISP0 flags. The vector table data determined for each interrupt request is the loaded into the

PC and branched.

Restoring from an interrupt is possible by using the RETI instruction.

R01UH0305EJ0200 Rev.2.00 706

Jul 04, 2013