RL78/G1A CHAPTER 22 SAFETY FUNCTIONS

Products

Code Flash Memory

(00000H to xxxxxH)

RAM

(zzzzzH to FFEFFH)

Detected Lowest Address for

Read/Instruction Fetch

(Execution) (yyyyyH)

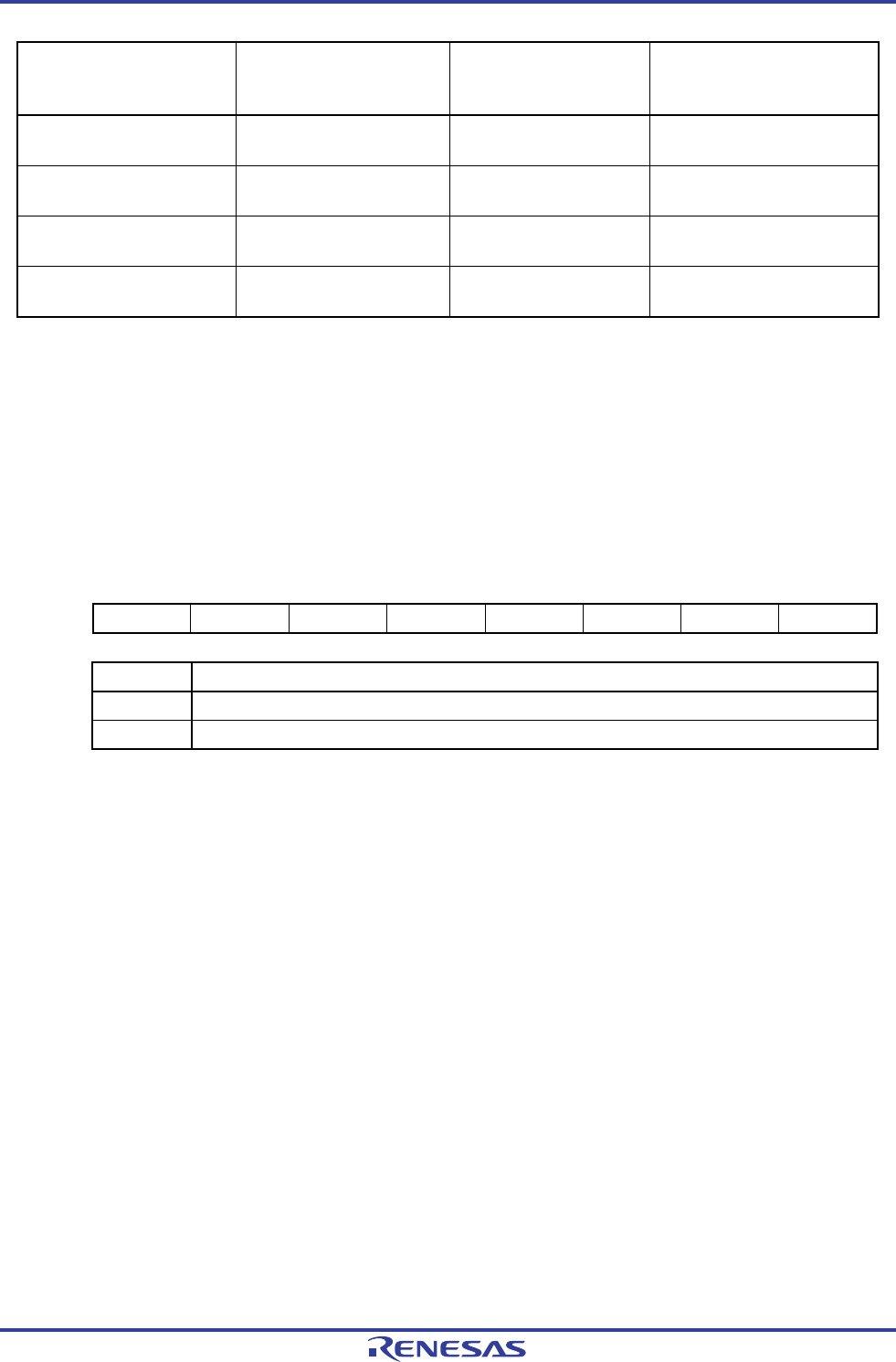

R5F10ExA (x = 8, B, G)

16384 × 8 bit

(00000H to 03FFFH)

2048 × 8 bit

(FF700H to FFEFFH)

10000H

R5F10ExC (x = 8, B, G, ,L)

32768 × 8 bit

(00000H to 07FFFH)

2048 × 8 bit

(FF700H to FFEFFH)

10000H

R5F10ExD (x = 8, B, G, L)

49152 × 8 bit

(00000H to 0BFFFH)

3072 × 8 bit

(FF300H to FFEFFH)

10000H

R5F10ExE (x = 8, B, G, L)

65536 × 8 bit

(00000H to 0FFFFH)

4096 × 8 bit

(FEF00H to FFEFFH)

10000H

22.3.6.1 Invalid memory access detection control register (IAWCTL)

This register is used to control the detection of invalid memory access and RAM/SFR guard function.

IAWEN bit is used in invalid memory access detection function.

The IAWCTL register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

Figure 22-12. Format of Invalid Memory Access Detection Control Register (IAWCTL)

Address: F0078H After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 0

IAWCTL IAWEN 0 GRAM1 GRAM0 0 GPORT GINT GCSC

IAWEN

Note

Control of invalid memory access detection

0 Disable the detection of invalid memory access.

1 Enable the detection of invalid memory access.

Note Only writing 1 to the IAWEN bit is enabled, not writing 0 to it after setting it to 1.

Remark By specifying WDTON = 1 (watchdog timer operation enable) for the option byte (000C0H), the invalid

memory access function is enabled even IAWEN = 0.

R01UH0305EJ0200 Rev.2.00 783

Jul 04, 2013