64

CHAPTER 3 CPU

●

Go to normal state (RUN) and reset

●

Go to/wake-up from standby mode

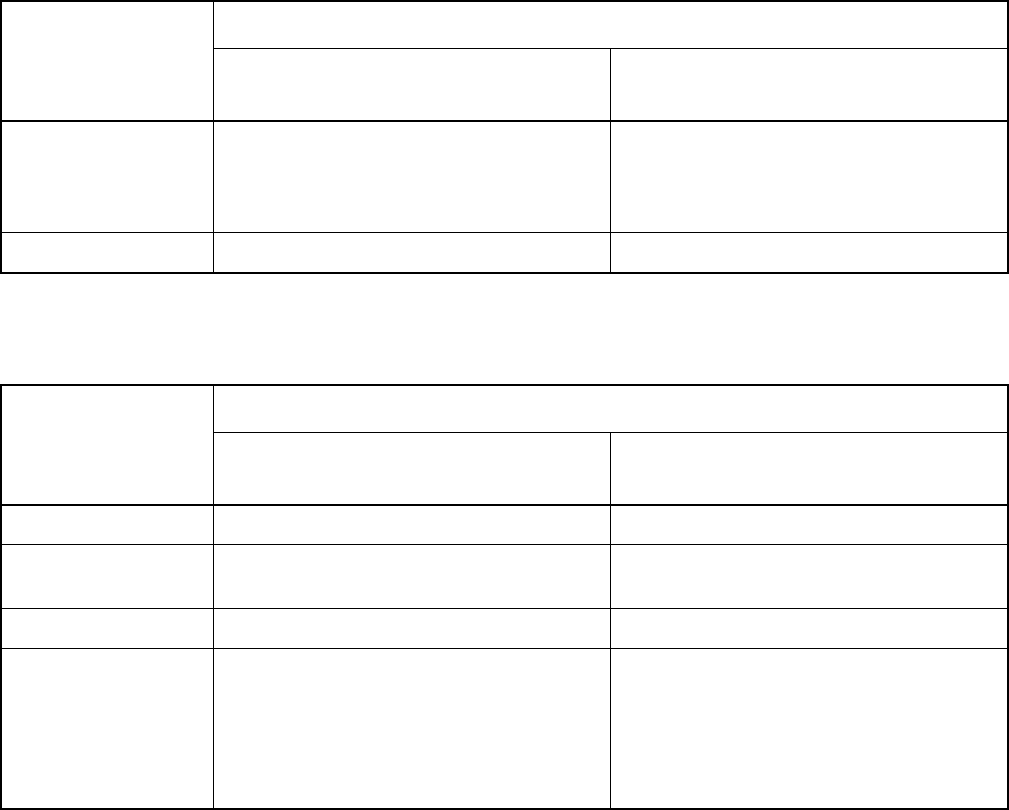

Table 3.7-3 Go to main clock mode run state and reset

State transition

Conditions/events required for transition

Products with power-on reset

(Figure 3.7-2 )

Products without power-on reset

(Figure 3.7-3 )

Go to normal state

(RUN) after power-on

[1] Main clock oscillation stabilization delay

time completes (timebase timer output).

[2] Wake-up from Reset input.

[1] External reset input must be held asserted

until main clock oscillation has had time to

stabilize.

[2] Wake-up from reset input de-asserted.

Reset in RUN state [3] Have external, software, or watchdog reset. [3] Have external, software, or watchdog reset.

Table 3.7-4 Go to/wake-up from standby mode

State transition

Conditions/events required for transition

Products with power-on reset

(Figure 3.7-2 )

Products without power-on reset

(Figure 3.7-3 )

Go to sleep mode [1] STBC: SLP = "1" [1] STBC: SLP = "1"

Wake-up from sleep

mode

[2] Interrupt

[3] External reset

[2] Interrupt

[3] External reset

Go to stop mode [4] STBC: STP = "1" [4] STBC: STP = "1"

Wake-up from stop

mode

[5] External interrupt

[6] Main clock oscillation stabilization delay

time completes (timebase timer output).

[7] External reset

[8] External reset (during oscillation

stabilization delay time)

[5] External interrupt

[6] Main clock oscillation stabilization delay

time completes (timebase timer output).

[7] External reset

[8] External reset (during oscillation

stabilization delay time)

STBC: Standby control register