105

CHAPTER 5 TIMEBASE TIMER

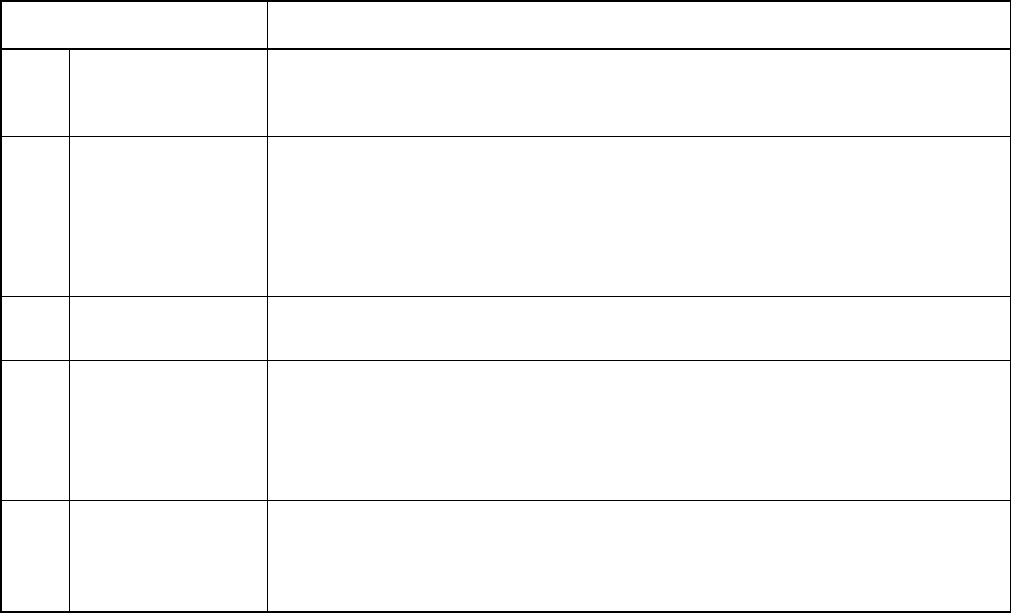

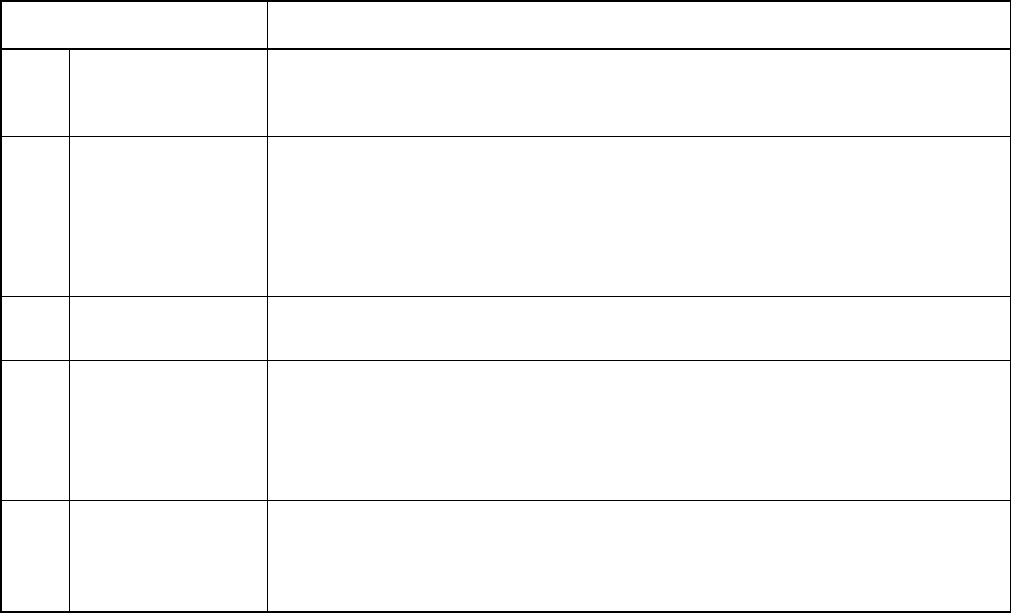

Table 5.3-1 Timebase timer control register (TBTC) bits

Bit Function

Bit 7

Bit 6

Bit 5

Unused bits • The read value is indeterminate.

• Writing to these bits has no effect on the operation.

Bit 4 TBIF:

Overflow interrupt

request flag bit

• This bit is set to "1" when counter overflow occurs on the specified bit of the timebase

timer counter.

• An interrupt request is generated when both this bit and the interrupt request enable bit

(TBIE) are "1".

• Writing "0" clears this bit.

• Writing "1" has no effect and does not change the bit value.

Bit 3 TBIE:

Interrupt request

• This bit enables or disables an interrupt request output to the CPU. An interrupt request

is output when both this bit and the overflow interrupt request flag bit (TBOF) are "1".

Bit 2 TBR:

Timebase timer

initialization bit

• This bit clears the timebase timer counter.

• Writing "0" to this bit clears the counter to "00000

H

". Writing "1" has no effect and

does not change the bit value.

Note:

The read value is always "1".

Bit 1

Bit 0

TBC1, TBC0:

Interval time

selection bits

• The read value is indeterminate.

• These bits select the cycle of the interval timer.

• These bits select which bit of the timebase timer counter to use as the interval timer bit.

• Four different interval times can be selected.