278

APPENDIX

B.4 Bit Manipulation Instructions (SETB, CLRB)

Some bits of peripheral function registers include bits that are read by a bit

manipulation instruction differently than usual.

■ Read-modify-write operation

By using these bit manipulation instructions, only the specified bit in a register or RAM location can be set

to 1 (SETB) or cleared to 0 (CLRB). However, as the CPU operates on data in 8-bit units, the actual

operation (read-modify-write operation) involves a sequence of steps: 8-bit data is read, the specified bit is

changed, and the data is written back to the location at the original address.

Table B.4-1 "Bus operation for bit manipulation instructions" shows bus operation for bit manipulation

instructions.

■ Read operation upon the execution of bit manipulation instructions

For some I/O ports and for the interrupt request flag bits, the value to be read differs between a normal read

operation and a read-modify-write operation.

●

I/O ports (during a bit manipulation)

From some I/O ports, an I/O pin value is read during a normal read operation, while an output latch value is

read during a bit manipulation. This prevents the other output latch bits from being changed accidentally,

regardless of the I/O directions and states of the pins.

●

Interrupt request flag bits (during a bit manipulation)

An interrupt request flag bit functions as a flag bit indicating whether an interrupt request exists during a

normal read operation. However, 1 is always read from this bit during a bit manipulation. This prevents the

flag from being cleared accidentally by a value of 0 which would otherwise be written to the interrupt

request flag bit when another bit is manipulated.

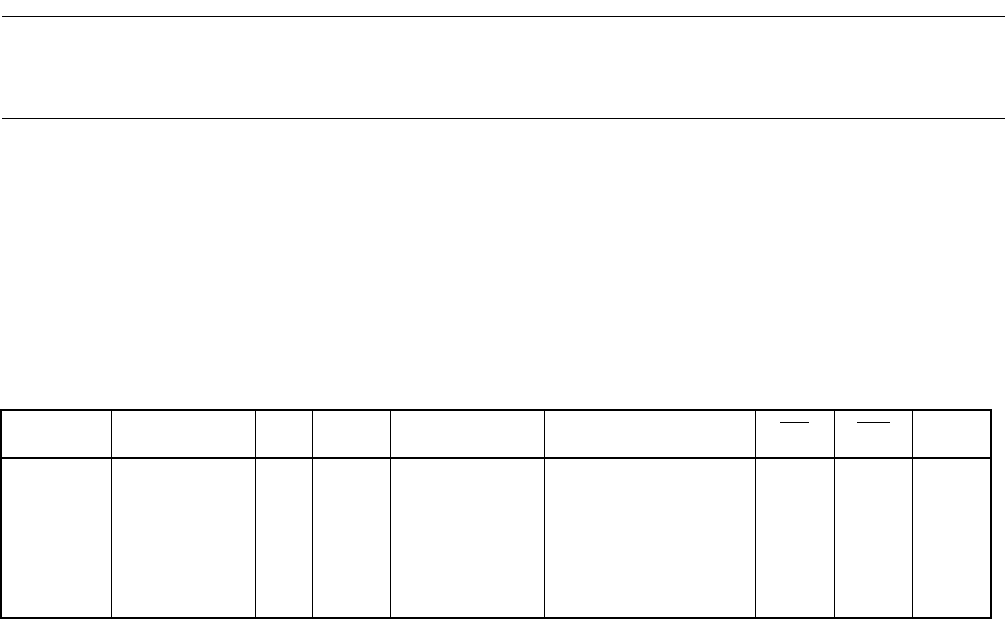

Table B.4-1 Bus operation for bit manipulation instructions

CODE MNEMONIC TO Cycle Address bus Data bus RD

WR RMW

A0 to A7 CLRB dir:b 4 1 N+1 dir 0 1 0

2 dir address Data 0 1 1

A8 to AF SETB dir:b 3 dir address Data 1 0 0

4 N+2 Next instruction 0 1 0