185

CHAPTER 9 8-BIT SERIAL I/O

9.7 States in Each Mode during 8-bit Serial I/O Operation

This section describes the operation of the 8-bit serial I/O when the device goes to

sleep or stop mode, or an operation halt request occurs during transfer.

■ Using internal shift clock

●

Operation in sleep mode

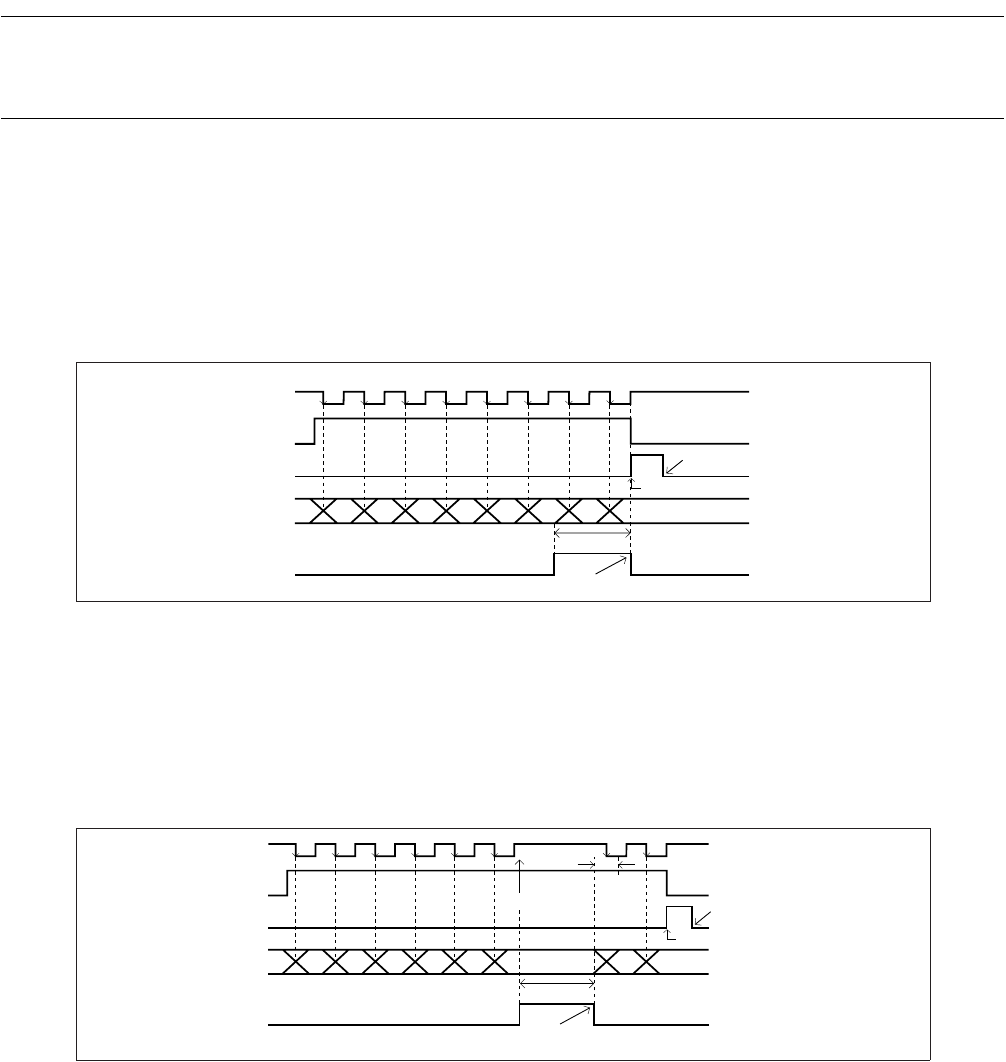

In sleep mode, serial I/O operation does not halt and transfer continues, as shown in Figure 9.7-1

"Operation in sleep mode (internal shift clock)".

Figure 9.7-1 Operation in sleep mode (internal shift clock)

●

Operation in stop mode

In stop mode, serial I/O operation and transfer stop, as shown in Figure 9.7-2 "Operation in stop mode halt

(internal shift clock)". As operation restarts after wake-up from stop mode, initialize the 8-bit serial I/O

depending on the state of the device with the 8-bit serial I/O is communicating.

Figure 9.7-2 Operation in stop mode halt (internal shift clock)

●

Operation during halt

Halting operation during transfer (SMR: SST = "0") halts the transfer and clears the shift clock counter, as

shown in Figure 9.7-3 "Operation during halt (internal shift clock)". Therefore, the device being

communicated with must also be initialized. In serial output operation, set data to the SDR register again

before reactivating.

#0 #1 #2 #3 #4 #5 #6 #7

SCK output

SST bit

SIOF bit

SO pin output

SLP bit

Cleared by the program.

Interrupt request

Sleep mode

Wake-up from sleep mode by IRQ5.

(STBC register)

#0 #1 #2 #3 #4 #5 #6 #7

Stop request

Oscillation stabilization

delay time

Wake-up from stop mode

by an external interrupt

SCK output

SST bit

SIOF bit

SO pin output

STP bit

Stop mode

Interrupt request

Cleared by the program.

(STBC register)