40

CHAPTER 3 CPU

3.4.4 Interrupt Processing Time

The total time from the generation of an interrupt request until control passes to the

interrupt processing routine is the sum of the time required to complete execution of

the current instruction and the interrupt handling time (the time required to prepare for

interrupt processing). The maximum time for this process is 30 instruction cycles.

■ Interrupt processing time

When an interrupt request occurs, the time until the interrupt is accepted and the interrupt processing

routine is executed includes the interrupt request sampling time and the interrupt handling time.

●

Interrupt request sampling time

Whether or not an interrupt request has occurred is determined by sampling and testing for interrupt

requests during the final cycle of each instruction. Therefore, the CPU is unable to identify interrupt

requests during execution of an instruction. The longest delay occurs when an interrupt request is generated

immediately after starting execution of a DIVU instruction, which has the longest instruction cycles (21

instruction cycles).

●

Interrupt handling time

Nine instruction cycles are required to perform the following preparation for interrupt processing after the

CPU accepts an interrupt request:

• Save the program counter (PC) and program status (PS).

• Set the top address of the interrupt processing routine (the interrupt vector) in the PC.

• Update the interrupt level bits (PS: CCR: IL1, IL0) in the program status (PS).

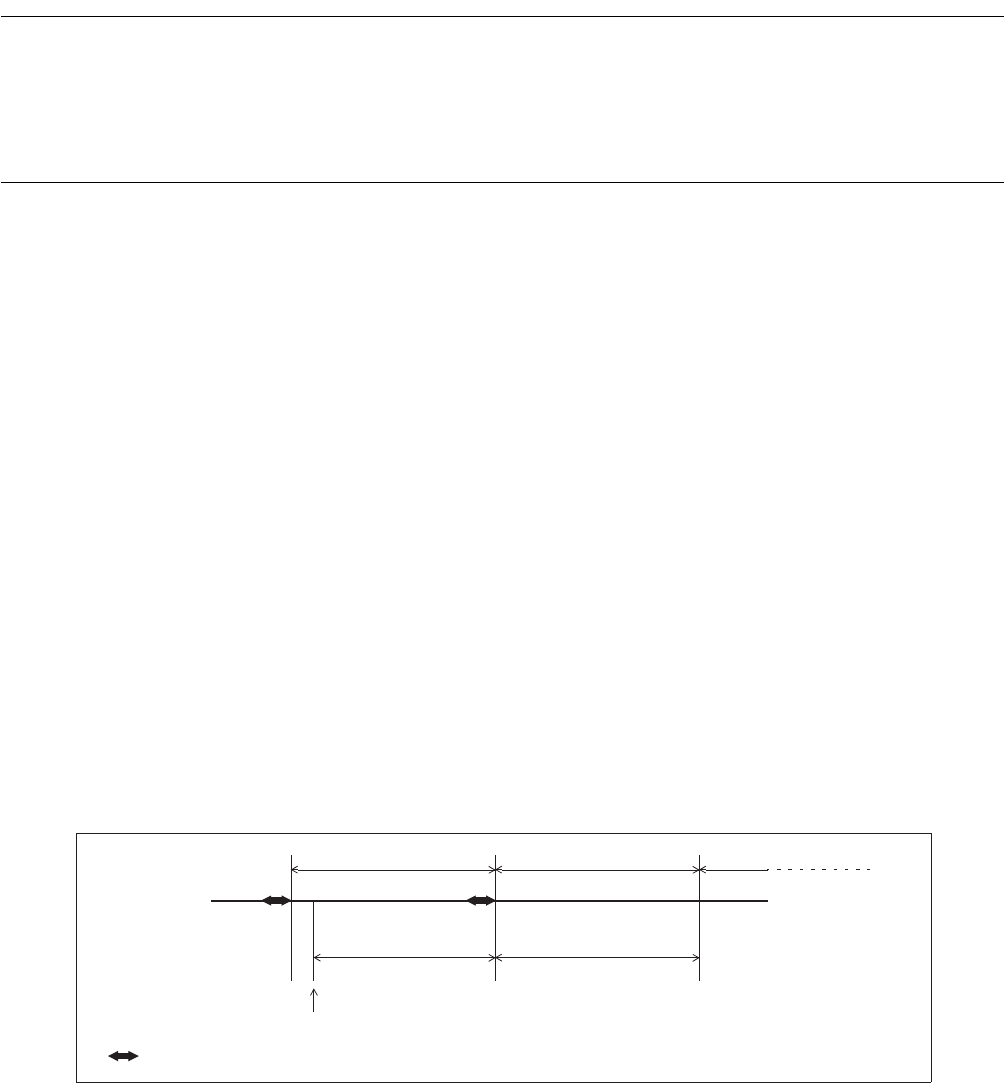

Figure 3.4-4 "Interrupt processing time" shows the interrupt processing time.

Figure 3.4-4 Interrupt processing time

The total interrupt processing time of 21 + 9 = 30 instruction cycles is required if an interrupt request

occurs immediately after starting execution of a DIVU instruction, which has the longest instruction cycles

(21 instruction cycles). If, on the other hand, the program does not use the DIVU or MULU instructions,

the maximum interrupt processing time is 6 + 9 = 15 instruction cycles.

The time of one instruction cycle changes with the clock mode and the main clock frequency as selected by

the "speed-shift" (gear) function. See Section 3.6 "Clocks" for details.

CPU operation

Interrupt waiting time

Execution of a standard instruction

Interrupt request

sampling time

Interrupt request occurs

Interrupt handling

Interrupt handling time

(9 instruction cycles)

Interrupt processing routine

: Final cycle of instruction. Interrupt requests are sampled at this timing.