218

CHAPTER 10 UART

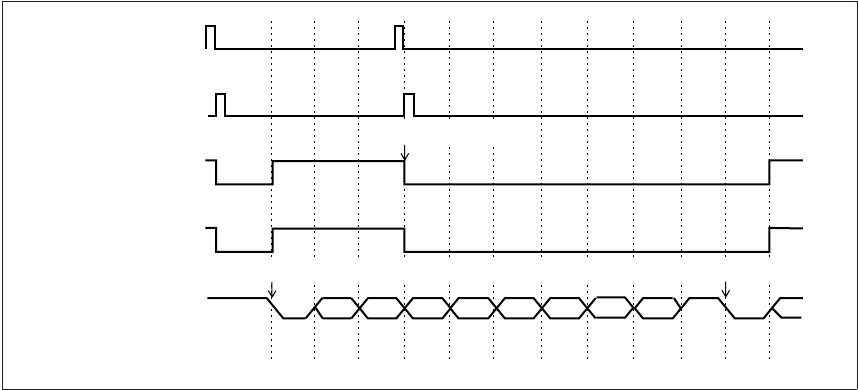

Figure 10.7-2 Transmit operation in mode 0, 1, 3

■ Receive operation

If receive data is received from the serial data input pin, a serial-parallel conversion process is initiated in

the internal receive shift register. After the data is normally (stop bit is detected), the receive data is

transferred from the internal shift register to the SIDR register and the RDRF bit is set to "1".

If an overrun or a framing error occurs, the receive data is not stored to the SIDR and the ORFE bit is set to

"1".

The RDRF and ORFE bits are set when the last stop bit is detected after the completion of the receive

operation. If the receive interrupt is enabled (SSD: RIE = "1"), an interrupt request (IRQ 4) is issued to the

CPU. If the RDRF bit is set, the receive data has already been stored to the SIDR register.

Figure 10.7-3 "Receive operation in mode 0, 1, 3", Figure 10.7-4 "Operation at overrun error in mode 0, 1,

3" and Figure 10.7-5 "Operation at framing error in mode 0, 1, 3" show receive operations non-parity and 1

stop bit.

Write to the SODR

(Interrupt processing routine)

TDRE

Transmit interrupt

Transmit data

SSD read

START

01234 56 7

STOP

START

Transfer the data to the transmit shift register. Transfer the data to the transmit shift register.

Transmit buffer full