215

CHAPTER 10 UART

10.5 UART Interrupts

The UART has three interrupt causes -- transfer error interrupt, receive data full

interrupt and transmit data empty interrupt:

• When receive data is transferred from the receive shift register to the serial input data

register (SIDR) (receive interrupt)

• When transmit data is transferred from the serial output data register (SODR) to the

transmit shift register (transmit interrupt)

■ Transmit interrupt

When transmission is enabled, writing transmit data to SODR register transfers the transmit data to the

transmit register. The transmit data is converted to serial in the transmit shift register and sent to the serial

data transmit pin (SO).

When the UART is ready to accept next data, the TDRE is set to "1", and an interrupt request (IRQ4) to the

CPU is generated if transmit interrupt request is enabled (SSD: TIE = "1").

■ Receive interrupt

When the data is received normally (stop bit is detected), the RDRF is set to "1".

When an overrun error, a framing error or a parity error occurs, their corresponding error flag bit is set to

"1". These bits are set when the stop bit(s) are detected, and an interrupt request (IRQ4) to the CPU is

generated if receive interrupt is enabled (SSD: RIE = "1").

■ Registers and vector tables for UART interrupts

See Section 3.4.2 "Interrupt Processing" for details on the interrupt operation.

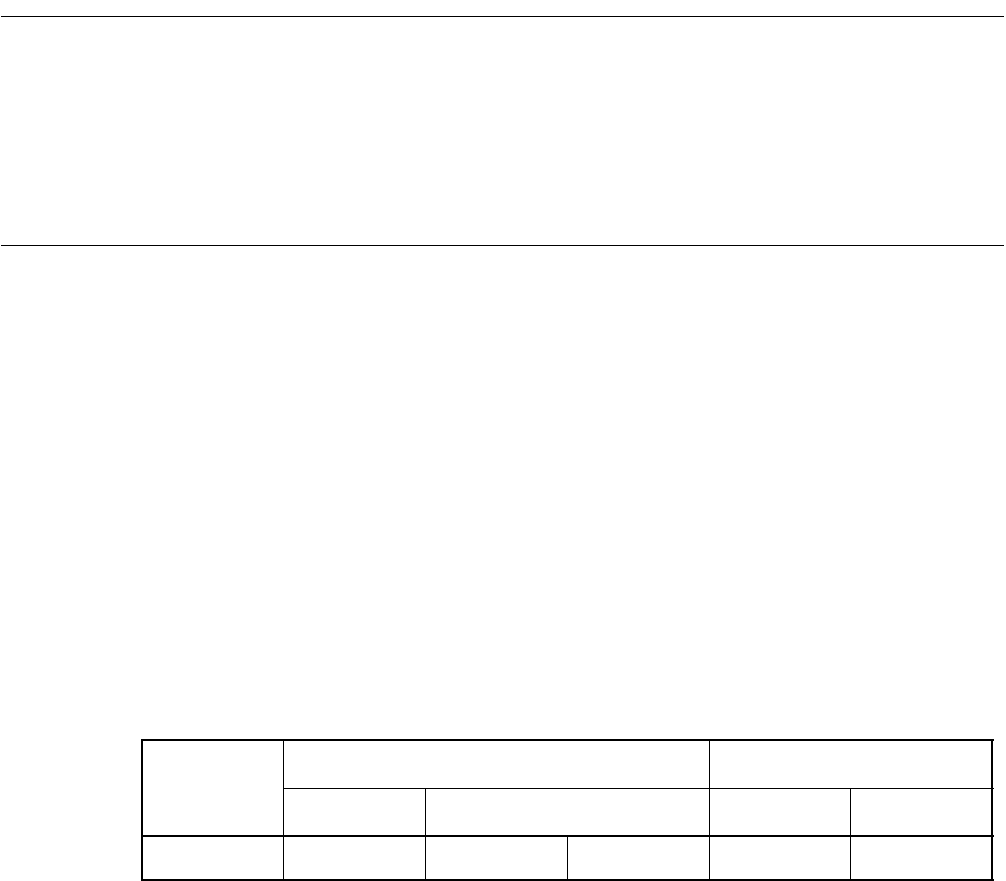

Table 10.5-1 Registers and vector tables for UART interrupts

Interrupt

Interrupt level setting register Vector table address

Register Setting bits Upper Lower

IRQ4 ILR2 (007D

H

) L41 (Bit 1) L40 (Bit 0) FFF2

H

FFF3

H