230

CHAPTER 11 EXTERNAL INTERRUPT CIRCUIT (EDGE)

11.4 External Interrupt Circuit Interrupts

The external interrupt circuit can generate interrupt requests when it detects a specified

edge on the signal input to an external interrupt pin.

■ Interrupts when the external interrupt circuit is operating

On detecting a specified edge on an external interrupt input, the external interrupt circuit sets the

corresponding external interrupt request flag bit (EIC: EIR0 - EIR1) to "1". An interrupt request to the CPU

(IRQ0 - IRQ1) is generated at this time if the corresponding interrupt request enable bit is enabled (EIC:

EIE0 - EIE1 = "1"). Always write "0" to the corresponding external interrupt request flag bit in the interrupt

processing routine to clear the interrupt request.

Note:

When enabling interrupts (EIE0 - EIE1 = "1") after exit of a reset, always clear the corresponding

external interrupt request flag bit (EIR0 - EIR1 = "0") at the same time.

Interrupt processing cannot return if the external interrupt request flag bit is "1" and the interrupt

request enable bit is enabled. Always clear the external interrupt request flag bit.

Reference:

Cancelling stop mode using an interrupt is only possible using the external interrupt circuit.

• An interrupt request is generated immediately if the external interrupt request flag bit is "1" when the

interrupt request enable bit is changed from disabled to enabled ("0" --> "1").

■ Register and vector table for the external interrupt circuit interrupts

See Section 3.4.2 "Interrupt Processing" for details on the operation of interrupts.

■ Notes when changing edge polarity selection

When changing the edge polarity for INT0 to INT1, always write "0" into the corresponding EIR bits. This

will prevent from accidentally creating an interrupt.

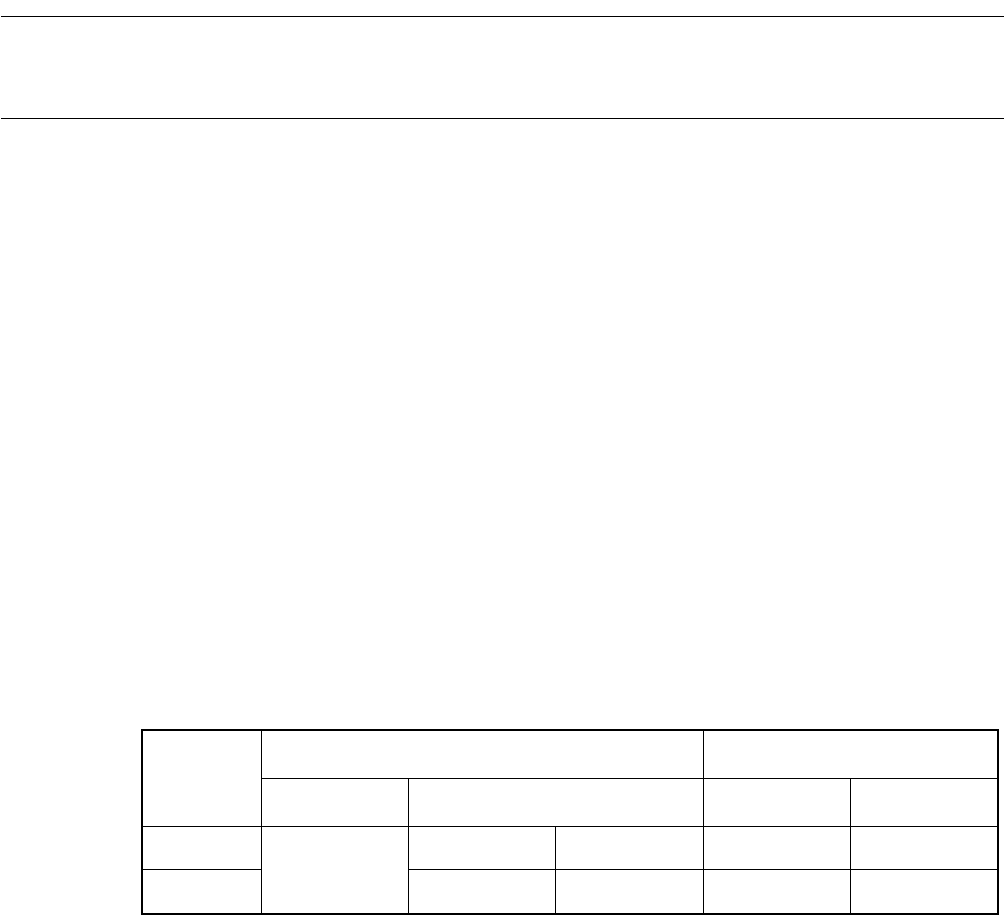

Table 11.4-1 Register and vector table for the external interrupt circuit interrupts

Interrupt

Interrupt level setting register Vector table address

Register Setting Bits Upper Lower

IRQ0

ILR1 (007C

H

)

L01 (Bit 1) L00 (Bit 0)

FFFA

H

FFFB

H

IRQ1 L11 (Bit 3) L10 (Bit 2)

FFF8

H

FFF9

H