149

CHAPTER 8 PULSE WIDTH COUNT TIMER (PWC)

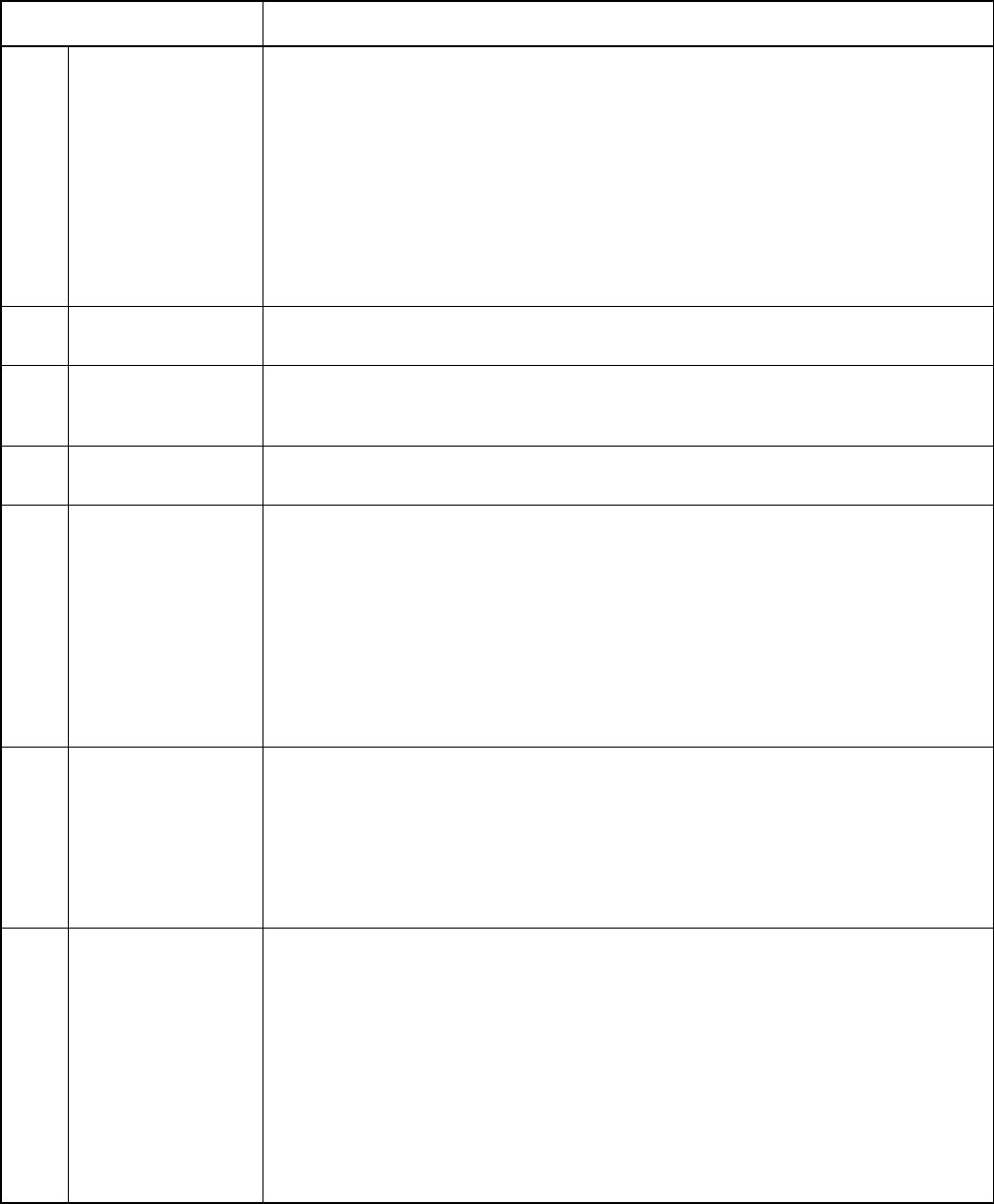

Table 8.3-1 PWC pulse width control register 1 (PCR1) bits

Bit Function

Bit 7 EN:

Counter operation

enable bit

• For the interval timer function:

Writing "1" to this bit starts the counter to count down from the PWC reload buffer register

(RLBR) value. Writing "0" to this bit stops the counter operation.

• For the pulse width measurement function:

Writing "1" to this bit enables measurement. The counter starts to count down from "FF

H

" on

detection of the specified edge on the measurement pulse. Writing "0" to this bit stops the

counter operation.

Note:

If operation is disabled (EN = "0") during measurement in pulse width measurement mode, the

counter stops but the value is not transferred to the RLBR register. Restarting operation (EN =

"1") sets the counter value to "FF

H

" then enables operation.

Bit 6 Unused bit • The read value is indeterminate.

• Writing to this bit has no effect on the operation.

Bit 5 IE:

Interrupt request enable

bit

• This bit enables or disables an interrupt request output to the CPU.

An interrupt request is output when both this bit and one or more of the interrupt request flag bits

(UF, IR, and BF) are "1".

Bit 4

Bit 3

Unused bits • The read value is indeterminate.

• Writing to these bits has no effect on the operation.

Bit 2 UF:

Underflow (01

H

-->

00

H

) interrupt request

flag bit

• This bit is set to "1" when the counter underflow (01

H

--> 00

H

) occurs.

An interrupt request is output when both this bit and the interrupt request enable bit (IE) are "1".

• Writing "0" clears this bit. Writing "1" has no effect and does not change the bit value.

Notes:

• When the interval timer function is active, the PWC inverts the timer output bit (PCR2: TO) if

the counter underflow (01

H

--> 00

H

) occurs. In reload timer mode, counting down continues

from the RLBR register value. In one-shot timer mode, the counter operation automatically stops

(EN = "0").

• If the counter underflow (01

H

--> 00

H

) occurs while measuring a long input pulse in the pulse

width measurement function, this bit is set to "1" and counter operation continues.

Bit 1 IR:

Measurement

completion interrupt

request flag bit

• For the pulse width measurement function:

This bit is set to "1" when the pulse width measurement is completed.

An interrupt request is output when both this bit and the interrupt request enable bit

(IE) are "1".

• Writing "0" clears this bit. Writing "1" has no effect and does not change the bit value.

• For the interval timer function:

The bit has no meaning.

Bit 0 BF:

Buffer full flag bit

• For the pulse width measurement function:

This bit is an interrupt request flag and is set to "1" when a measurement value is

present in the RLBR register.

An interrupt request is output when both this bit and the interrupt request enable bit

(IE) are "1".

This bit is set to "1" when pulse width measurement completes and cleared to "0" when

the measurement value is read from the RLBR register.

This bit is read-only. The write value has no meaning and has no effect on the

operation.

• For the interval timer function:

This bit has no meaning.