210

CHAPTER 10 UART

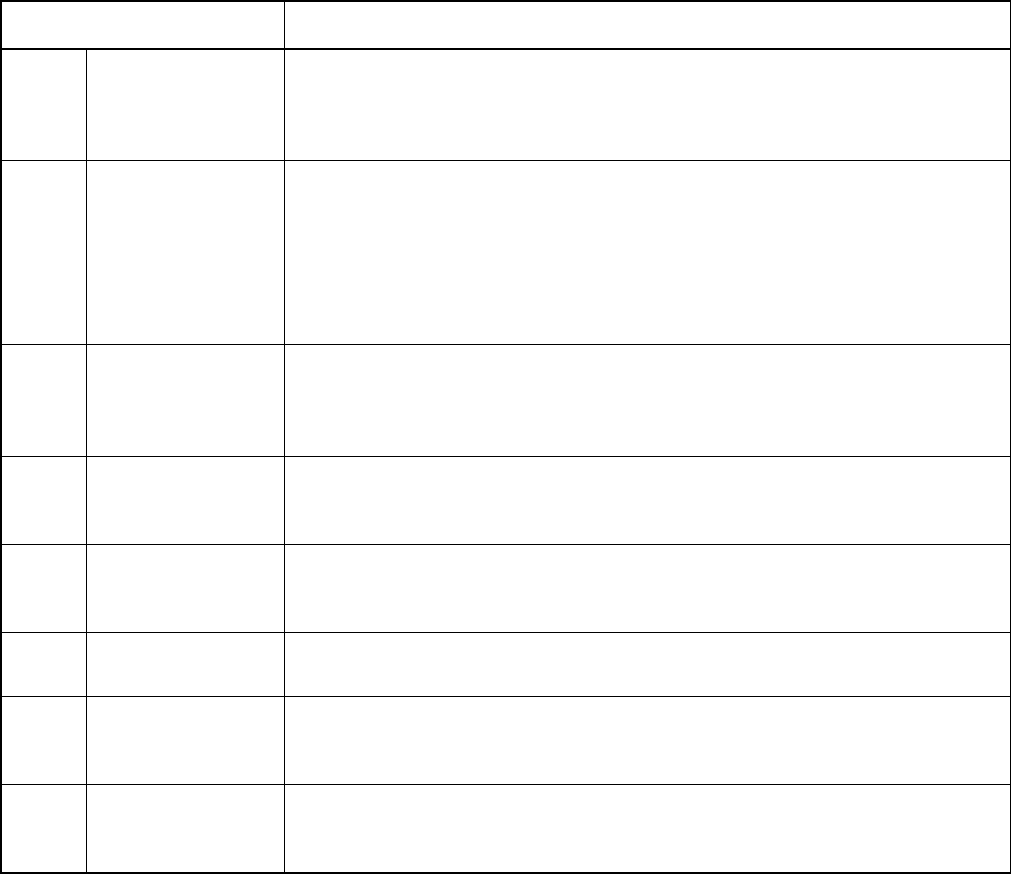

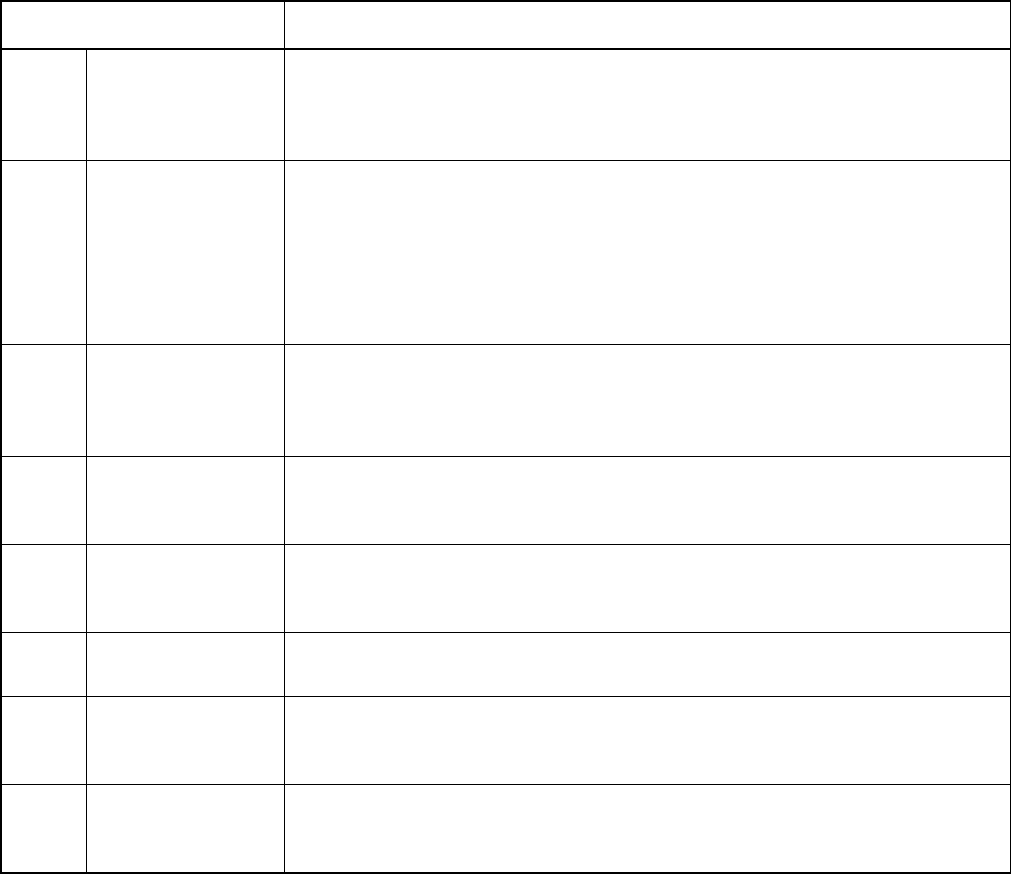

Table 10.4-3 Serial status and data register (SSD) bits

Bit Function

Bit 7 RDRF:

Receive data register

full bit

• This flag represents the status of the serial input data register (SIDR).

• This flag is set when receiving data is loaded into the SIDR register. It is cleared

when the SIDR register is read. If the RDRF bit is set when the RIE bit is "1", a

receive interrupt request is generated.

Bit 6 ORFE:

Overrun/Framing

error flag bit

• This bit is set when overrun or framing error is generated during receiving.

• If this flag is set, data is not transferred from the receive shift register to SIDR

register.

• When the SIDR register is read after reading the SSD register with the ORFE flag set

to "1", the ORFE flag is cleared to "0".

• If the ORFE bit is set when the RIE bit is "1", a receive interrupt request is

generated.

Bit 5 TDRE:

Transmission data

register empty bit

• This flag represents the status of the serial output data register (SODR).

• This flag is cleared when transmission data is written into the SODR register. It is set

when the data is loaded into the transmit shifter and transmission begins. If the

TDRE bit is set when the TIE bit is "1", a transmission interrupt request is generated

Bit 4 TIE:

Transmitter interrupt

enable bit

• This bit enables transmission interrupt. If the TDRE bit is "1", a transmission

interrupt is immediately generated once transmission interrupt enable bit is set to

"1".

Bit 3 RIE:

Receiver interrupt

enable bit

• This bit enables receive interrupt. If the RDRF bit is "1" or if any error flag is "1", a

receive interrupt is immediately generated once receive interrupt enable bit is set to

"1".

Bit 2 Unused bit • The read value is indeterminate.

• Writing to this bit has no effect on the operation.

Bit 1

TD8/TP:

Transmitted data

parity selection bit

• This bit is used to select the parity for the transmitted data.

Bit 0 RD8/RP:

Received data parity

selection bit

• This bit is used to select the parity for the received data.