151

CHAPTER 8 PULSE WIDTH COUNT TIMER (PWC)

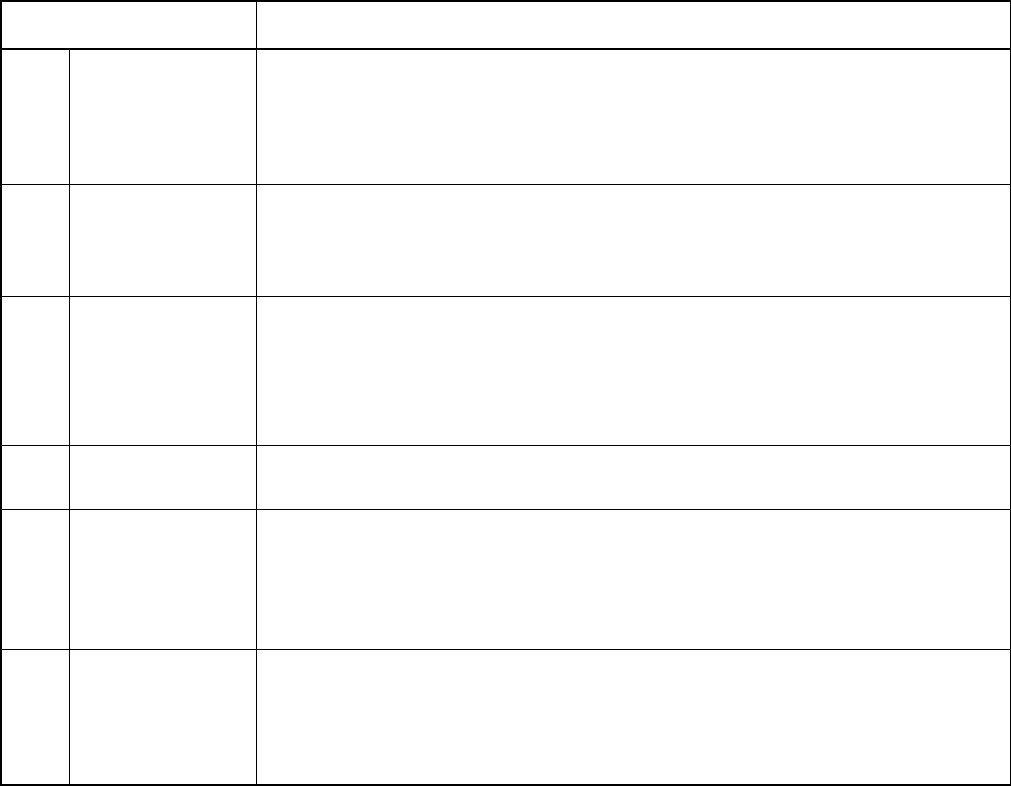

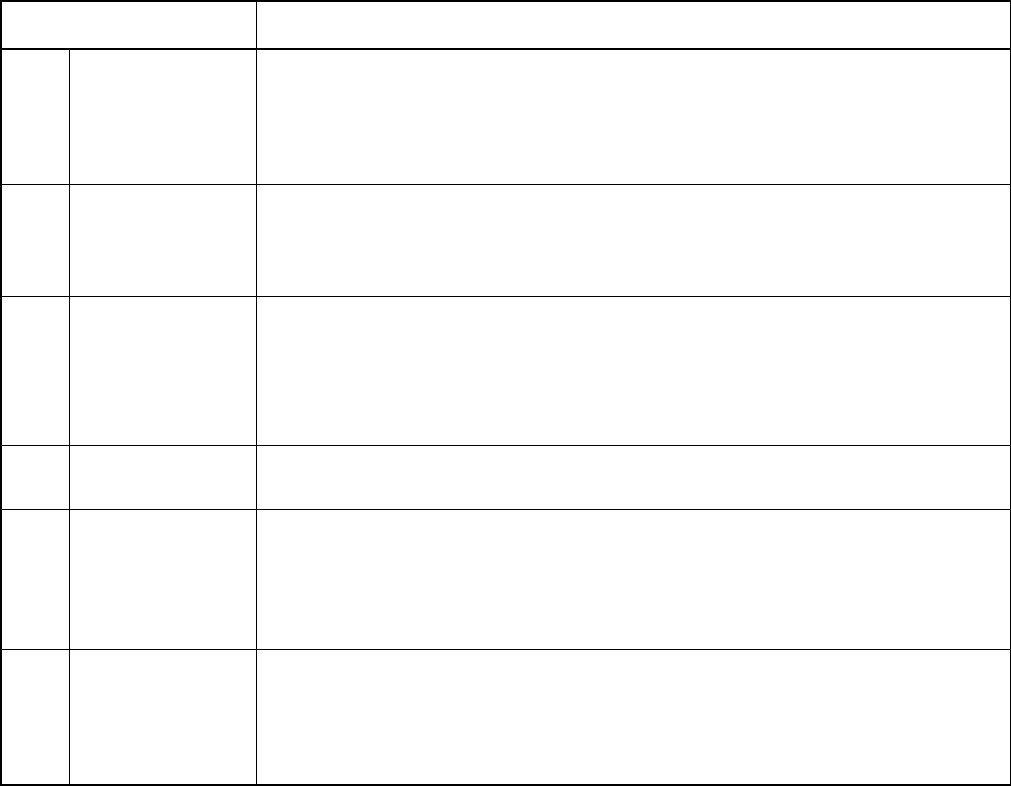

Table 8.3-2 PWC pulse width control register 2 (PCR2) bits

Bit Function

Bit 7 FC:

Operating mode

selection bit

• This bit switches between the interval timer function (FC = "0") and pulse width

measurement function (FC = "1").

Note:

When using the pulse width measurement function (FC = "1"), set the P42/PWC/INT1

pin as an input port.

Bit 6 RM:

Reload mode

selection bit

• For the interval timer function:

This bit selects reload timer mode (RM = "0") or one-shot timer mode (RM = "1").

• For the pulse width measurement function:

This bit has no meaning.

Bit 5 TO:

Timer output bit

• The value of this bit is inverted each time a counter value underflow (01

H

--> 00

H

)

occurs.

• By counting the number of times this bit is inverted (number of underflow (01

H

--> 00

H

)

occurs), pulse widths longer than 2

8

× the cycle of the selected count clock can be

measured.

Bit 4 Unused bit • The read value is indeterminate.

• Writing to this bit has no effect on the operation.

Bit 3

Bit 2

C1, C0:

Count clock

selection bits

• These bits select the count clock for the interval timer function and pulse width

measurement function.

• Three internal count clocks can be selected.

Note:

Do not set "11

B

" to C1 and C0 bits.

Bit 1

Bit 0

W1, W0:

Measured pulse

selection bits

• For the pulse width measurement function:

These bits select which pulse edges to use as the start and end conditions for pulse

measurement. Four types of pulse width or cycle can be selected.

• For the interval timer function:

These bits have no meaning.

Note:

Do not modify the PCR2 register while the counter is operating (PCR1: EN = "1").