104

CHAPTER 5 TIMEBASE TIMER

5.3 Timebase Timer Control Register (TBTC)

The timebase timer control register (TBTC) is used to select the interval times bit, clear

the counter, control interrupts, and check the state of the timebase timer.

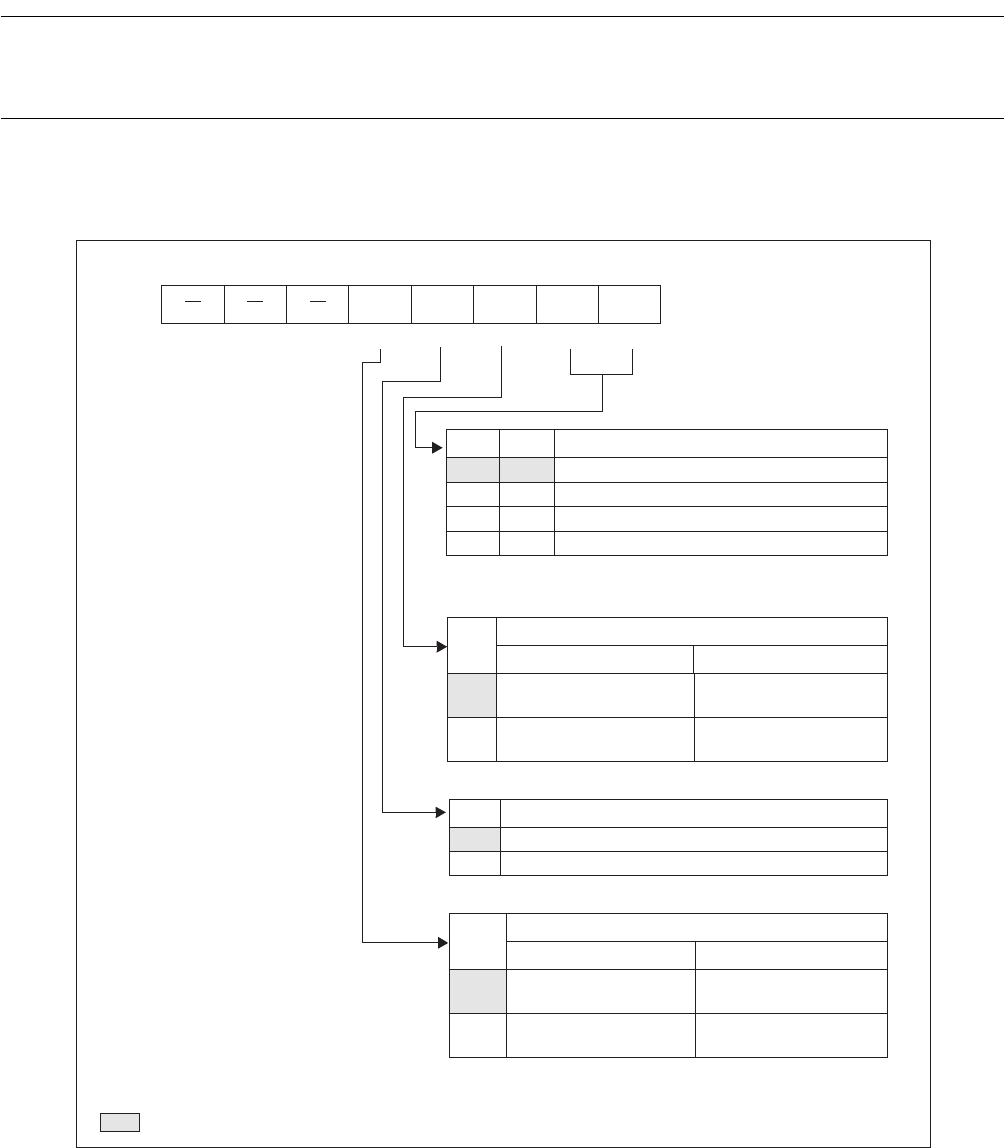

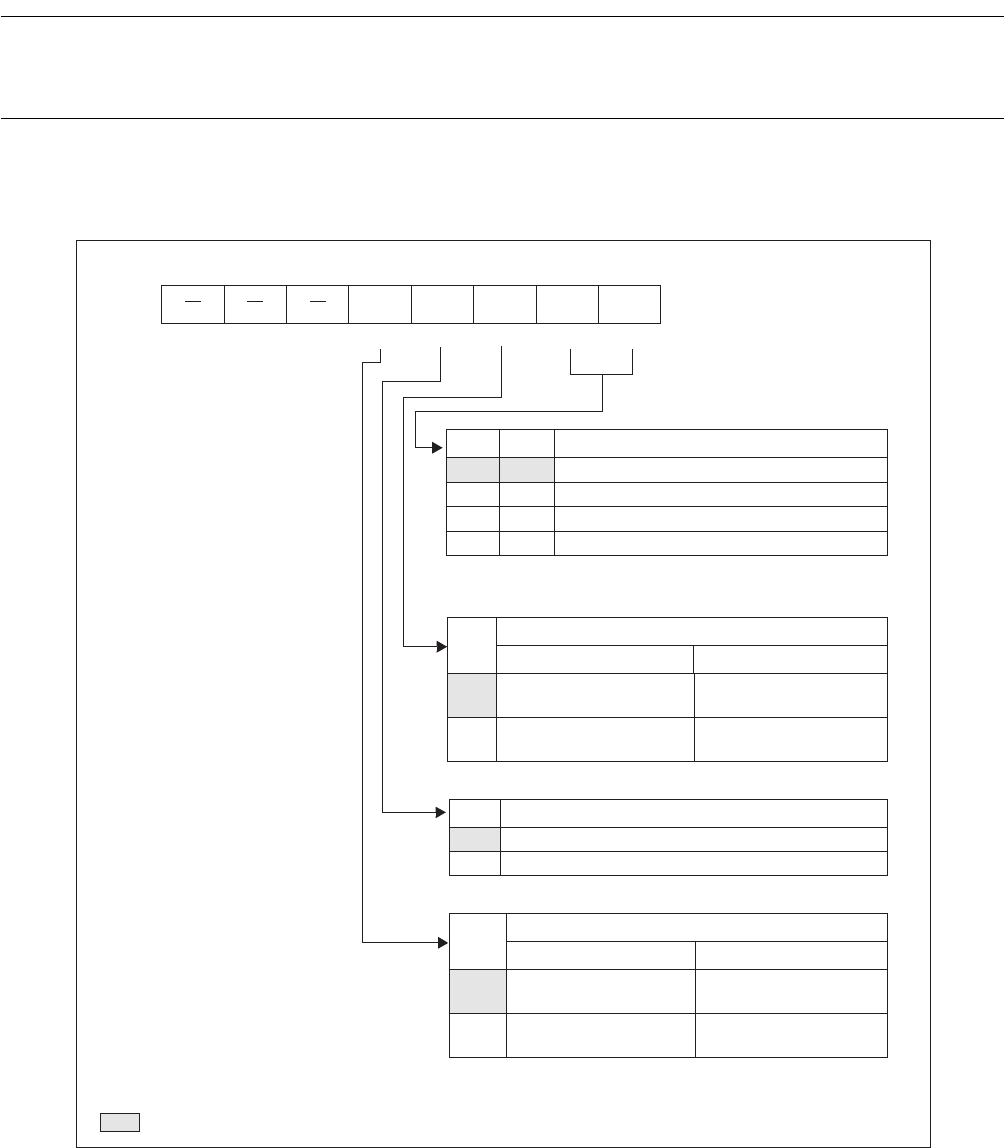

■ Timebase timer control register (TBTC)

Figure 5.3-1 Timebase timer control register (TBTC)

Address Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Initial value

000A

H

TBIF TBIE TBR TBC1 TBC0

---00000

B

R/W R/W W R/W R/W

TBC1 TBC0 Interval time selection bits

0 0

2

15

/F

CH

01

2

17

/FCH

10

2

19

/F

CH

11

2

21

/F

CH

TBR

Timebase timer initialization bit

Read Write

0 —

Clears timebase timer

counter

1

Reading always returns

"1".

No effect. The bit does

not change.

TBIE Interrupt request enable bit

0 Disables interrupt request output.

1 Enables interrupt output.

TBIF

Overflow interrupt request flag bit

Read Write

0

No overflow on specified

bit.

Clears this bit.

1 Overflow on specified bit.

No effect. The bit does

not change.

R/W :Readable and writable

W :Write-only

— : Unused

: Initial value

FCH: Main clock oscillation frequency