180

CHAPTER 9 8-BIT SERIAL I/O

9.4 8-bit Serial I/O Interrupts

The 8-bit serial I/O can generate interrupt requests after completion of the serial input

and output of the 8-bit data.

■ Interrupt for serial output operation

The 8-bit serial I/O performs the serial input operation and serial output operation at the same time. When

the serial transfer starts, the data in the serial data register (SDR) is input and output one bit at a time,

synchronized with the cycle of the selected shift clock. The interrupt request flag bit (SMR: SIOF) is set to

"1" on the rising edge of the shift clock of the eighth bit.

At this time, an interrupt request (IRQ5) to the CPU is generated if the interrupt request enable bit is

enabled (SMR: SIOE = "1").

Write "0" to the SIOF bit in the interrupt processing routine to clear the interrupt request. The SIOF bit is

set after completing 8-bit serial output, regardless of the SIOE bit value.

Reference:

The interrupt request flag bit is not set (SMR: SIOF = "1") if serial transfer is stopped (SMR: SST =

"0") at the same time as serial data transfer completes for the serial I/O operation. An interrupt request

is generated immediately if the SIOF bit is "1" when the SIOE bit is changed from disabled to enabled

("0" --> "1").

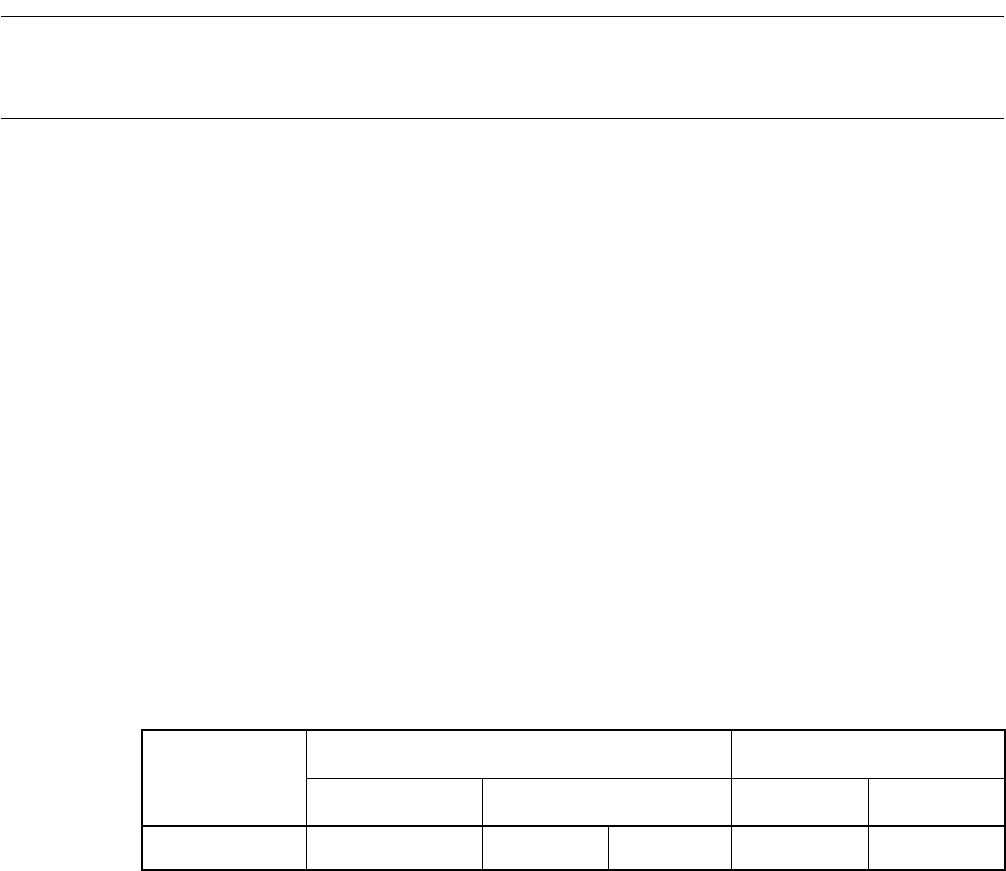

■ Register and vector table for 8-bit serial I/O interrupts

See Section 3.4.2 "Interrupt Processing" for details on the interrupt operation.

Table 9.4-1 Register and vector table for 8-bit serial I/O interrupts

Interrupt

Interrupt level setting register Vector table address

Register Setting bits Upper Lower

IRQ5 ILR2 (007D

H

) L51 (Bit 3) L50 (Bit 2) FFF0

H

FFF1

H