188

CHAPTER 9 8-BIT SERIAL I/O

9.8 Notes on Using 8-bit Serial I/O

This section lists points to note using when the 8-bit serial I/O.

■ Notes on using 8-bit serial I/O

●

Error on starting serial transfer

Activating the serial transfer by software (SMR: SST = "1") is not synchronized with the falling edge

(output) or rising edge (input) of the shift clock, there is a delay of up to one cycle of the selected shift

clock before the first serial data I/O occurs.

●

Malfunction due to noise

In serial data transfer, malfunction of the serial I/O may occur if unwanted pulses (pulses exceeding the

hysteresis width) occur on the shift clock due to external noise.

●

Notes on setting by program

• Write to the serial mode register (SMR) and serial input register (SDR) when serial I/O is stopped

(SMR: SST = "0").

• Do not modify other SMR register bits when starting/enabling serial I/O transfer (SMR: SST = "1").

• When using an external shift clock and when serial data output is enabled (SMR: SOE = "1"), the output

level on the SO pin when the external shift clock is the most significant bit (when MSB first is selected)

or least significant bit (when LSB first is selected). This applies even if serial transfer is stopped (SMR:

SST = "0").

• The interrupt request flag bit (SMR: SIOF) is not set if serial I/O transfer is stopped (SMR: SST = "0")

at the same time as serial transfer data completes.

• Interrupt processing cannot return if the SIOF bit is "1" and the interrupt requests enable bit is enabled

(SIOE = "1"). Always clear the SIOF bit.

●

Idle state of shift clock

Hold the external shift clock at the "H" level during the delay time between transfers of 8-bit data (idle

state). When set as the shift clock output (SMR: SCKE = "1"), the internal shift clock (SMR: CKS1, CKS0

= other than "11

B

") output an "H" level during the idle state.

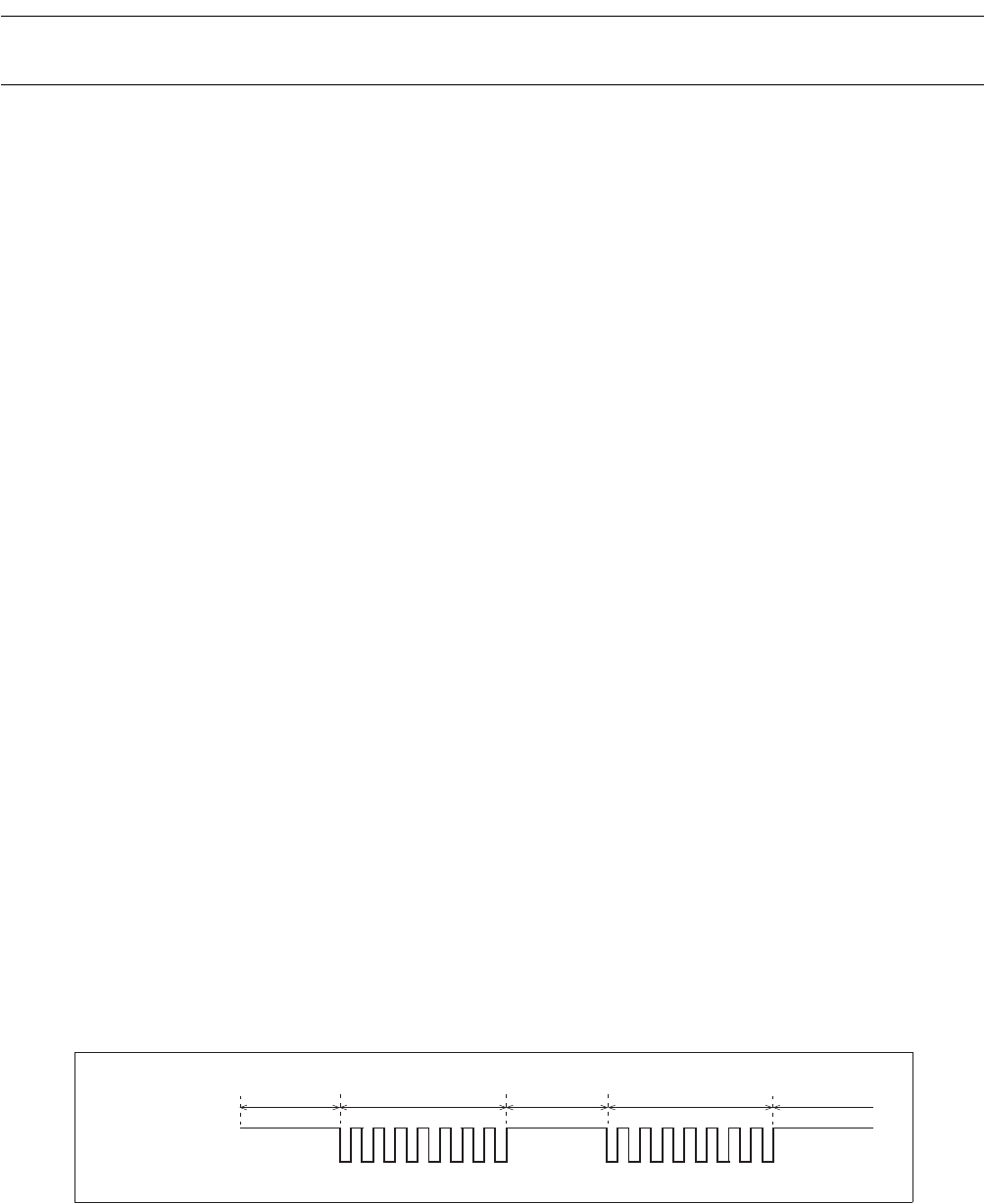

Figure 9.8-1 "Idle state of shift clock " shows the idle state of the shift clock.

Figure 9.8-1 Idle state of shift clock

Idle state

External shift clock

8-bit data transfer Idle state

Idle state

8-bit data transfer