199

CHAPTER 10 UART

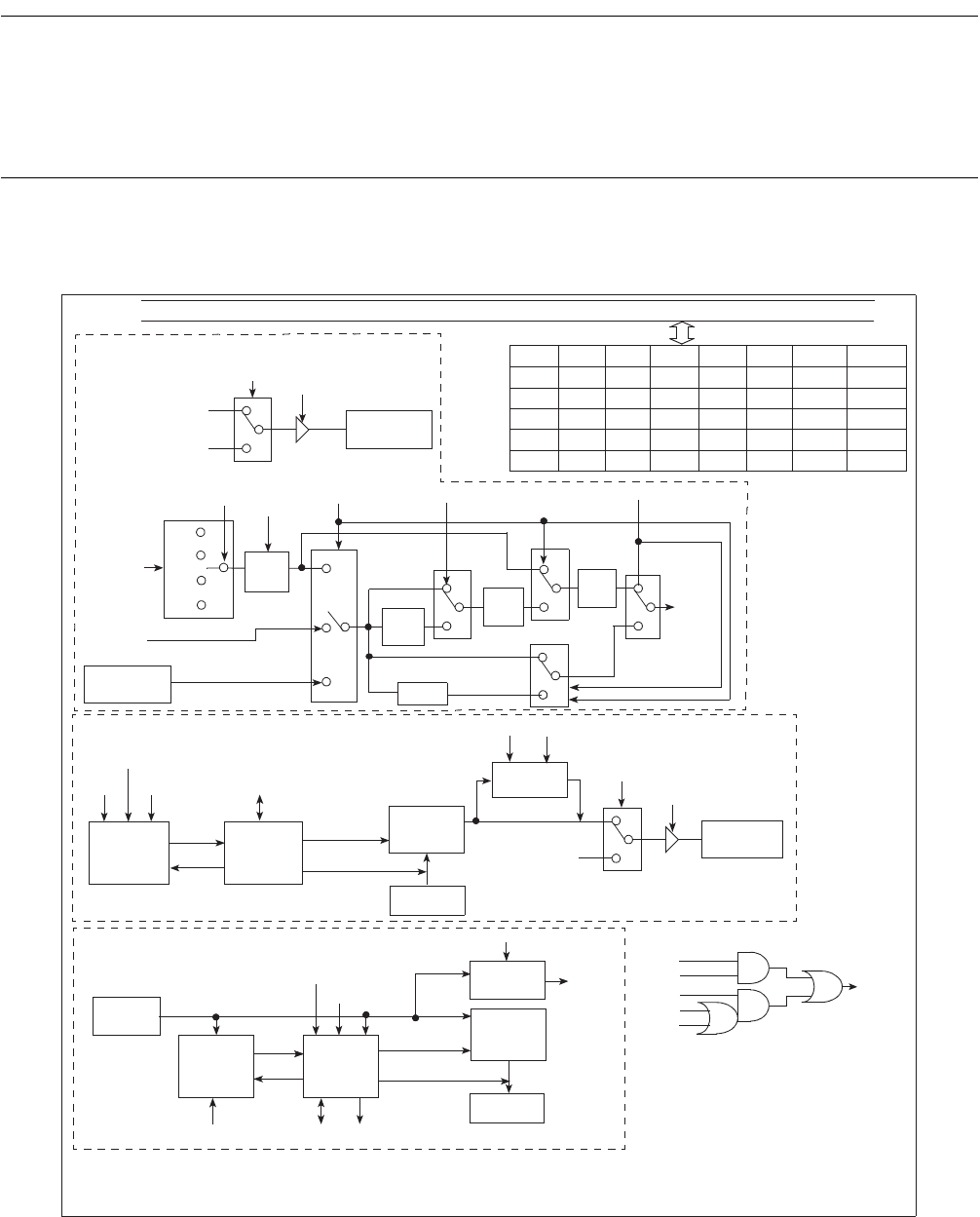

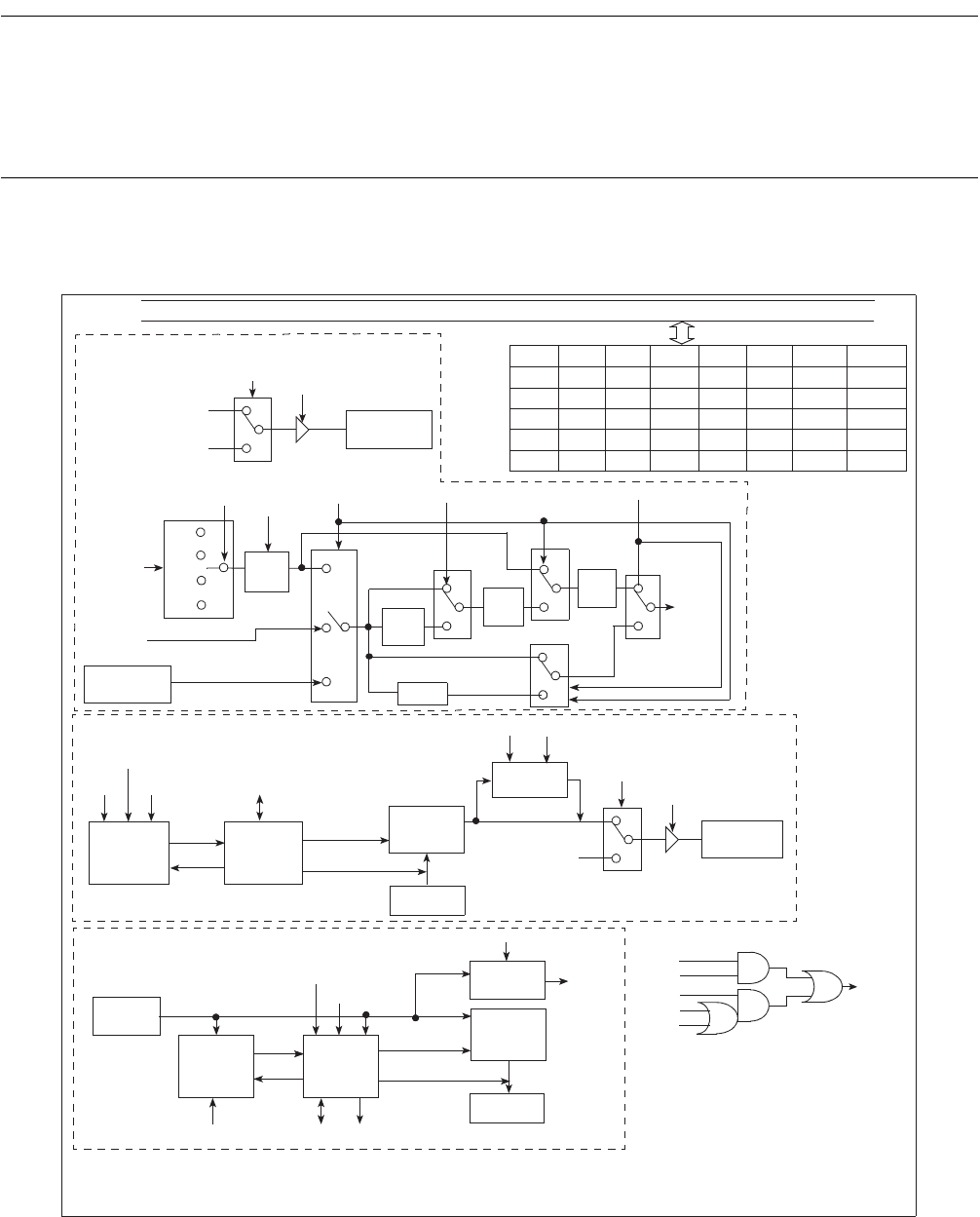

10.2 Structure of UART

The UART consists of the following blocks:

• Baud rate generator and serial clock generator

• Data transmitter and data receiver

• Registers (SMC1, SMC2, SRC, SSD, SIDR, SODR)

■ Block diagram of UART

Figure 10.2-1 Block diagram of UART

P45/SCK

CPU clock

1/4

1/6

1/13

1/65

PDS1

PDS0

PWM timer

output

1/2

n

1/4

1/2

1/8

RC2

RC1

RC0

CS1

CS0

CR

SMDE

UART serial clock

RSEL

SCKE*

1

Serial I/O clock

P45/SCK

1/2

Serial

clock

Baud rate generator and serial clock generator

Data transmit control circuit

Data receive control circuit

P43/SI

Start bit

detection

Start

Reset

Receiver

byte count

Shift clock

Transfer clock

Shifter

SIDR

Parity

generator

CR

RDRF

ORFE

Transmitter

byte count

Timing

Reset

Transmitter

control

Shift clock

Transfer clock

Shifter

SODR

Parity

generatorTDRE

RD8/RP

RSEL

SOE*

2

P44/SO

Serial I/O data

PEN

MC1

MC0

PEN

TD8/TP

MC1

MC0

SBL

ORFE

RDRF

RIE

TDRE

TIE

Internal data bus

Registers:

SMC1 PEN SBL MC1 MC0

SMDE —

SCKE SOE

SMC2

——

PSEN

—

RSEL

—

PDS1 PDS0

SSD RDRF ORFE TDRE TIE RIE

—

TD8/TP

RD8/RP

SRC

——

CR CS1 CS0 RC2 RC1 RC0

SODR

SIDR

IRQ4

*1: At switching between port output and serial clock output, the SCKE bit of the UART is valid when the RSEL bit is 0; the SCKE bit of the serial I/O is

valid when the RSEL bit is 1.

*2: At switching between port output and serial data output, the SOE bit of the UART is valid when the RSEL bit is 0; the SOE bit of the serial I/O is

valid when the RSEL bit is 1.