172

1745D–ATARM–04-Nov-05

AT91M55800A

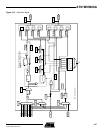

19.5.4 TC Channel Mode Register: Capture Mode

Register Name: TC_CMR

Access Type: Read/Write

Reset State: 0

Offset: 0x04

• TCCLKS: Clock Selection

• CLKI: Clock Invert (Code Label TC_CLKI)

0 = Counter is incremented on rising edge of the clock.

1 = Counter is incremented on falling edge of the clock.

• BURST: Burst Signal Selection

• LDBSTOP: Counter Clock Stopped with RB Loading (Code Label TC_LDBSTOP)

0 = Counter clock is not stopped when RB loading occurs.

1 = Counter clock is stopped when RB loading occurs.

• LDBDIS: Counter Clock Disable with RB Loading (Code Label TC_LDBDIS)

0 = Counter clock is not disabled when RB loading occurs.

1 = Counter clock is disabled when RB loading occurs.

31 30 29 28 27 26 25 24

– – – – – – – –

23 22 21 20 19 18 17 16

– – – –

LDRB LDRA

15 14 13 12 11 10 9 8

WAVE=0 CPCTRG

– – –

ABETRG ETRGEDG

7 6 5 4 3 2 1 0

LDBDIS LDBSTOP BURST CLKI TCCLKS

TCCLKS Clock Selected Code Label: TC_CLKS

0 0 0 MCK/2 TC_CLKS_MCK2

0 0 1 MCK/8 TC_CLKS_MCK8

0 1 0 MCK/32 TC_CLKS_MCK32

0 1 1 MCK/128 TC_CLKS_MCK128

1 0 0 MCK/1024 TC_CLKS_MCK1024

1 0 1 XC0 TC_CLKS_XC0

1 1 0 XC1 TC_CLKS_XC1

1 1 1 XC2 TC_CLKS_XC2

BURST Selected BURST Code Label: TC_BURST

0 0 The clock is not gated by an external signal. TC_BURST_NONE

0 1 XC0 is ANDed with the selected clock. TC_BURST_XC0

1 0 XC1 is ANDed with the selected clock. TC_BURST_XC1

1 1 XC2 is ANDed with the selected clock. TC_BURST_XC2