5-2 SYNCHRONIZATION OF DIGITAL FACILITIES

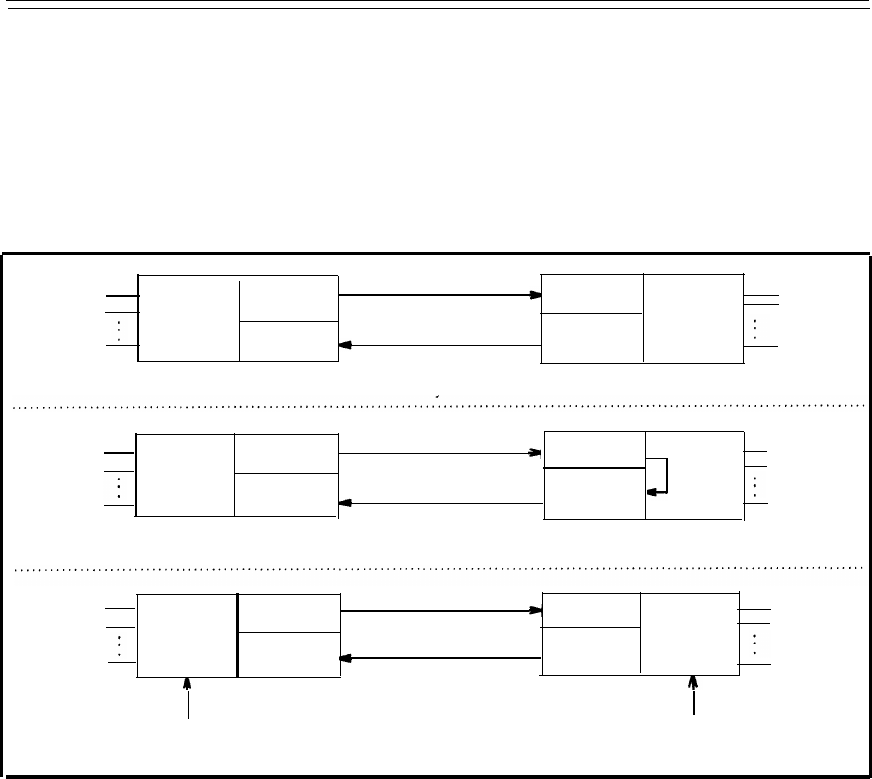

Figure 5-1-A, Options for Synchronization, shows one possible connection between a pair of D4-

channel banks. Such a connection (using D4-channel banks) can typically be found with a pair of

analog switching systems connected by T1-carrier facilities. For this arrangement, the transmitting

portion of each channel bank independently determines the clock rates. The receiving portion of

each channel bank derives its clock from the incoming digital bit stream. In this arrangement, the

channel banks convert the received digital signal directly to analog, and there is no requirement that

the two clock frequencies precisely match as the channel bank does not interface to another digital

system.

F

TRANSMIT

0

RECEIVE

F

CHANNEL

BANK

ANALOG

CHANNEL

BANK

0

ANALOG

F

TRANSMIT

RECEIVE

1

F

DIGITAL BIT STREAM

1

A: Not Synced

F

DIGITAL

SWITCHING

SYSTEM

0

TRANSMIT

RECEIVE

DIGITAL

CHANNEL

BANK

DIGITAL

TRANSMIT

F

F

0

RECEIVE 0

F

0

DIGITAL BIT STREAM

B: Loop Timed

F

DIGITAL

SWITCHING

SYSTEM

0

RECEIVE

TRANSMIT

DIGITAL

SWITCHING

SYSTEM

DIGITAL

DIGITAL

F

F

TRANSMIT

RECEIVE

0

F

0

DIGITAL BIT STREAM

0

C: Externally Synced

REFERENCE

CLOCK RATE F

REFERENCE

CLOCK RATE F

0

0

Figure 5-1. Options for Synchronization

Figure 5-1-B, Options for Synchronization, shows a different connection between a channel bank and

a digital switching system. For this configuration, the digital switch transmits a digital bit stream at

the rate (F0) that is determined by its internal clock. The digital switch must receive the incoming

digital bit stream at this same rate (F0). Otherwise, the switch’s receiving buffer may eventually

overrun or underrun.

NOTE: Switching is done by placing the signals from individual time slots on one link into the

time slots on other links using a process called time-slot interchange (TSI). For this process to

work properly, bit synchronization must be maintained on all links terminating on the digital

switching node, no matter where the links originate.

If the average transmit rate is faster than the average receive rate, the receive buffer will eventually

overrun. If the average receive bit-clock rate is faster than the average transmit bit-clock rate, the

receive buffer will eventually underrun. It is necessary to prevent overruns (deletions) and underruns

(repetitions) by synchronizing the network properly. Improper synchronization results in buffers

repeating or deleting bits in 1-frame increments.