PicoBlaze 8-bit Embedded Microcontroller www.xilinx.com 93

UG129 (v1.1.2) June 24, 2008

AND sX, Operand — Logical Bitwise AND Register sX with Operand

R

Pseudocode

if (CARRY = 1) then

sX Å (sX + Operand + 1) mod 256; always an 8-bit result

else

sX Å (sX + Operand) mod 256 ; always an 8-bit result

end if

if ( (sX + Operand + CARRY) > 255 ) then

CARRY Å 1

else

CARRY Å 0

endif

if ( ((sX + Operand + CARRY) = 0) or ((sX + Operand + CARRY) = 256) )

then

ZERO Å 1

else

ZERO Å 0

endif

PC Å PC + 1

Registers/Flags Altered

Registers: sX, PC

Flags: CARRY, ZERO

Notes

pBlazIDE Equivalent: ADDC

AND sX, Operand — Logical Bitwise AND Register sX with

Operand

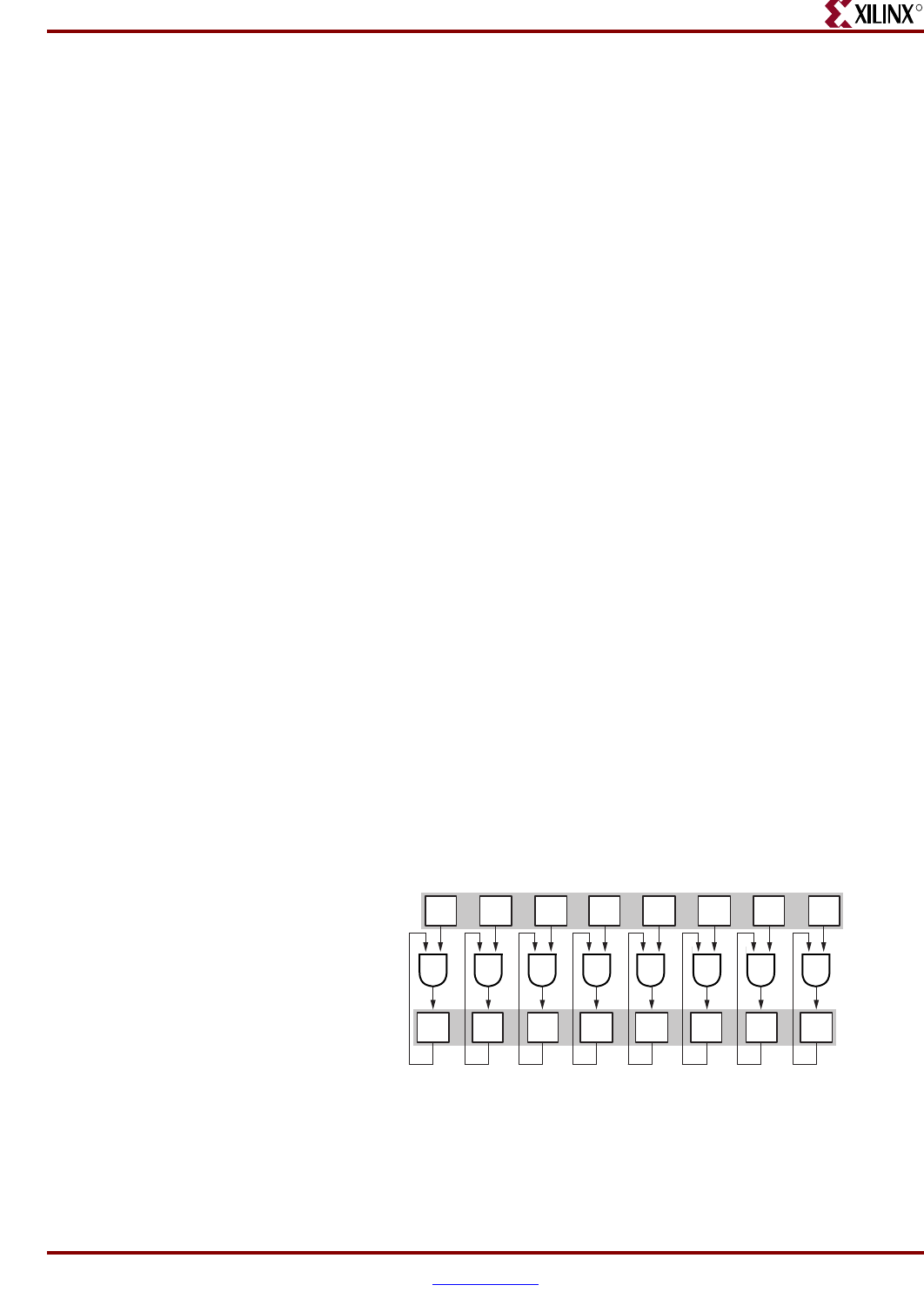

The AND instruction performs a bitwise logical AND operation between two operands, as

shown in Figure C-3. The first operand is any register, which also receives the result of the

operation. A second operand is also any register or an 8-bit immediate constant. The ZERO

flag is set if the resulting value is zero. The CARRY flag is always cleared by an AND

instruction.

The AND operation can be used to perform tests on the contents of a register. The status of

the ZERO flag then controls the flow of the program.

Figure C-3: AND Operation

7 6 5 4 3 2 1 0

7 6 5 4 3 2 1 0

Register sX

Register sY

Literal kk

UG129_aC_06_051604