56 www.xilinx.com PicoBlaze 8-bit Embedded Microcontroller

UG129 (v1.1.2) June 24, 2008

Chapter 6: Input and Output Ports

R

Pipelining for Maximum Performance

In most applications, the PicoBlaze microcontroller has more than sufficient performance

to meet application requirements. However, PicoBlaze designs attached to multiple

memory blocks or that have many simple ports may end up using most, if not all, of the 256

available port addresses. Decoding and routing all 256 locations complicates the overall

design, especially for designs requiring maximum performance.

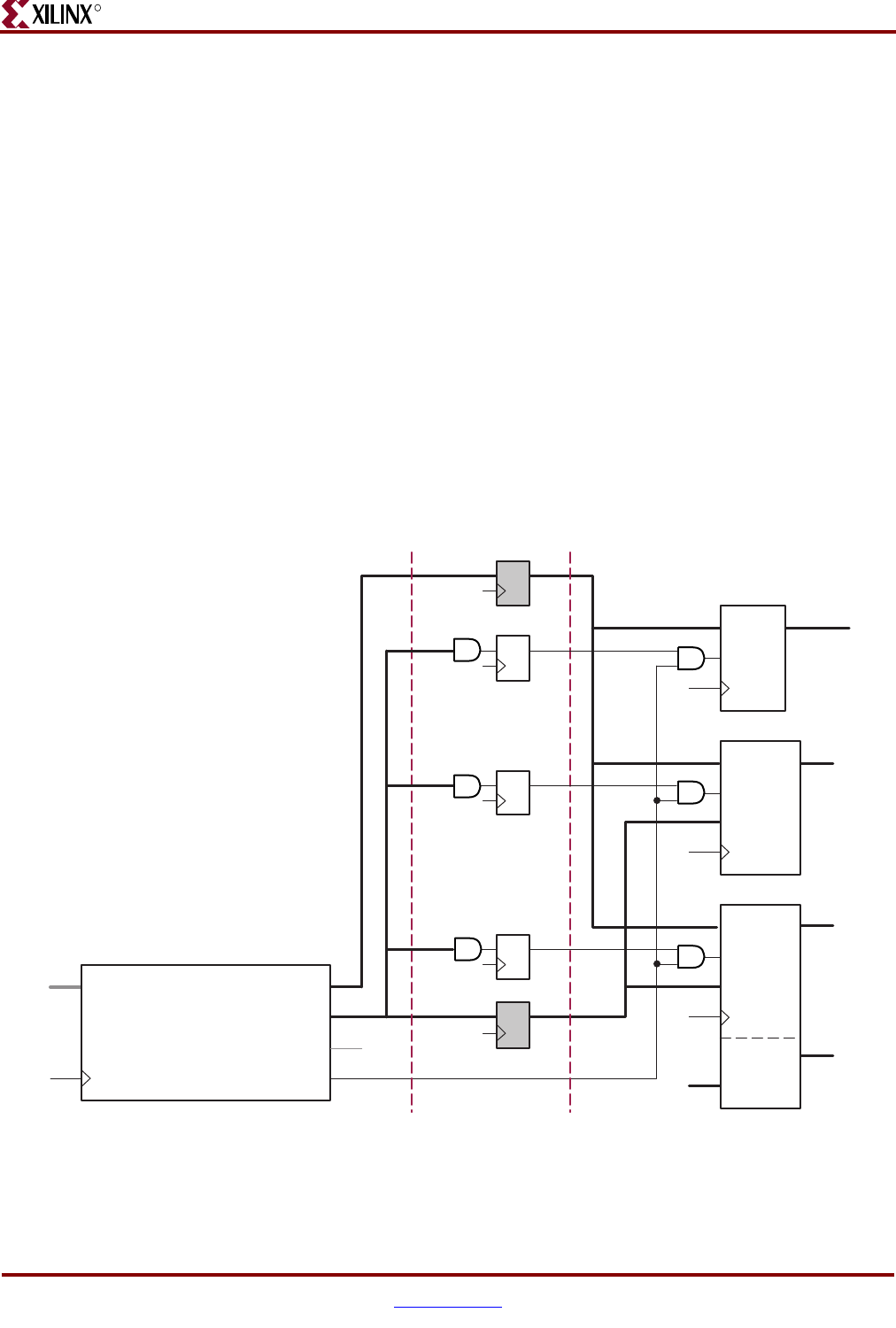

Pipelining the PORT_ID decoding function improves overall system performance. During

an OUTPUT operation, both the PORT_ID and OUT_PORT ports are valid for two clock

cycles while the WRITE_STROBE output is only active during the second of the two cycles,

as shown Figure 6-6.

One approach to improving interface performance is to pipeline the PORT_ID decoding

logic, as illustrated in Figure 6-9. In designs with many ports, the fanout and loading on

the PORT_ID bus limits maximum performance. Fortunately, because the PORT_ID port is

active for two clock cycles, the PORT_ID logic can be pipelined. Each decoded PORT_ID

value is then captured in a flip-flop. Each pipelined decode value is qualified using the

WRITE_STROBE signal during the next clock cycle to actually capture the OUT_PORT

data.

Figure 6-9: Pipelining the PORT_ID Decoding Improves Performance

IN_PORT[7:0] OUT_PORT[7:0]

PORT_ID[7:0]

READ_STROBE

WRITE_STROBE

PicoBlaze Microcontroller

EN

DQ

WE

D SPO

A[4:0]

RAM16X1D (x8)

DPO

DPRA[4:0]

WE

DO

A[4:0]

RAM32X1S (x8)

Clock Cycle 1

Decode Address

Clock Cycle 2

Qualify with WRITE_STROBE

DECODE

DECODE

DECODE

UG129_c6_08_052004