PicoBlaze 8-bit Embedded Microcontroller www.xilinx.com 43

UG129 (v1.1.2) June 24, 2008

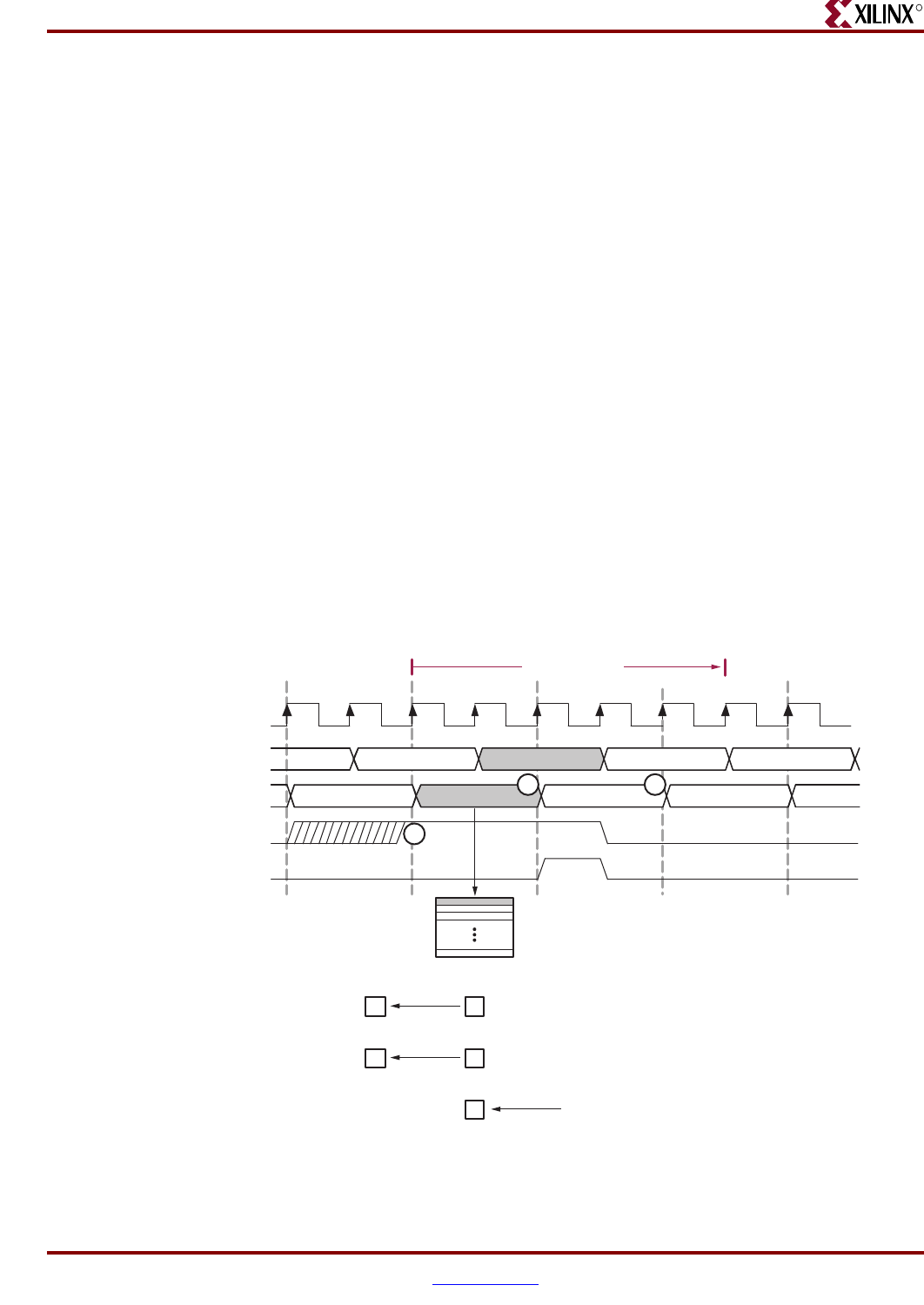

Example Interrupt Flow

R

3. The PicoBlaze microcontroller recognizes the interrupt and preempts the ADD s0,s1

instruction. The current PC, which points to the ADD s0 s1 instruction, is pushed

onto the CALL/RETURN stack. Likewise, the ZERO and CARRY flags are preserved.

Furthermore, the INTERRUPT_ENABLE flag is cleared disabling any further

interrupts. Finally, the PC is loaded with all ones (3FF) and the PicoBlaze

microcontroller performs an interrupt service routine call to the last location in the

instruction store. If using a 1Kx18 block RAM for instruction store, the last location is

3FF. If using a smaller instruction store, then the interrupt vector is still located in the

last instruction location. The PicoBlaze microcontroller also asserts the

INTERRUPT_ACK output, indicating that the interrupt is being acknowledged.

4. The interrupt vector is always located in the last location in the instruction store. In this

example, the program jumps to the interrupt service routine (ISR) via the JUMP isr

instruction.

5. When completed, exit the interrupt service routine (ISR) using the special RETURNI

instruction. Do not use the RETURN instruction, which is used with normal subroutine

calls. The RETURNI ENABLE instruction returns from the interrupt service routine and

re-enables the INTERRUPT input, which was automatically disabled when the

interrupt was recognized. Using RETURNI DISABLE also returns from the interrupt

service routine but leaves the INTERRUPT input disabled.

6. The RETURNI instruction restores the preserved ZERO and CARRY flags saved

during Step (3). Likewise, the RETURNI instruction pops the top of the

CALL/RETURN stack into the PC, which causes the PicoBlaze microcontroller to

resume program executing the instruction that was preempted by the interrupt, ADD

s0,s1 in this example.

Figure 4-3: Interrupt Timing Diagram

ADD s0,s1INPUT s1,01 JUMP isr TEST s7,02

3FF isr

Address of

ADD s0,s1

...

Interrupt

recognized

Call to interrupt

vector, assert

INTERRUPT_ACK

Jump to interrupt

service routine

ADD s0,s1 instruction

pre-empted. PC saved to

stack. Flags preserved.

Interrupt disabled.

Begin executing

interrupt service

routine

5 clock cycles

CLK

INSTRUCTION

ADDRESS[9:0]

INTERRUPT

INTERRUPT_ACK

PREEMPTED

CALL/RETURN

Stack

Preserved

ZERO Flag

ZERO

Flag

Preserved

CARRY Flag

CARRY

Flag

INTERRUPT_ENABLE

1

0

UG129_c4_03_051404

2

3 4