PicoBlaze 8-bit Embedded Microcontroller www.xilinx.com 33

UG129 (v1.1.2) June 24, 2008

Processing Data

R

Each bit of register sX is logically ANDed with either the contents of register sY or a literal

constant, kk. The operation sets the ZERO flag if the result of all bitwise AND operations

is zero.

If the second operand contains a single ‘1’ bit, then the CARRY flag tests if the

corresponding bit in register sX is ‘1’ as shown in the example in Figure 3-23.

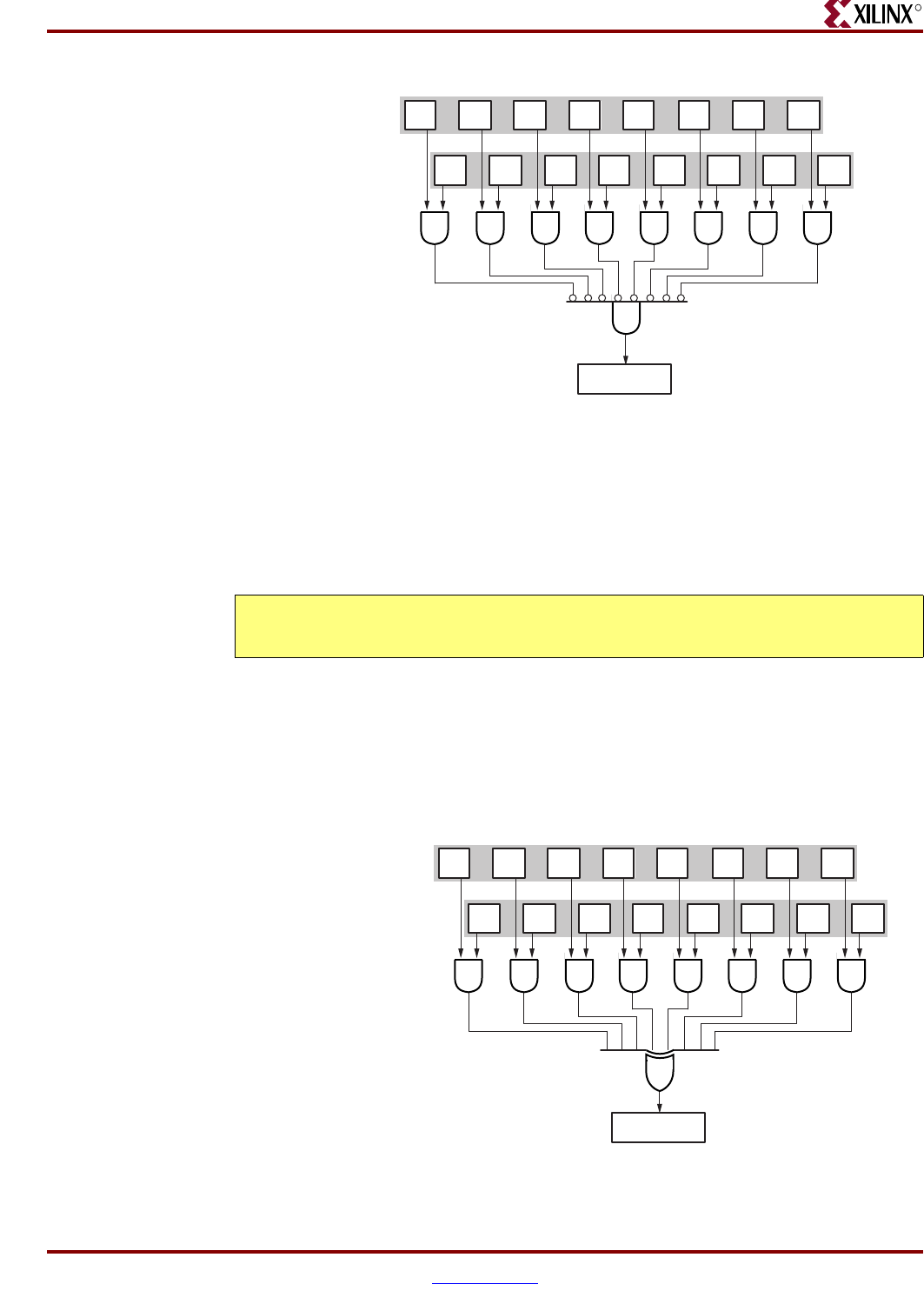

In a broader application, the CARRY bit generates the odd parity for the included bits in

register sX, as shown in Figure 3-24. The second operand acts as a mask. If a bit in the

second operand is ‘0’, then the corresponding bit in register sX is not included in the

generated parity value. If a bit in the second operand is ‘1’, then the corresponding bit in

register sX is included in the final parity value.

Figure 3-22: The TEST Instruction Affects the ZERO Flag

Figure 3-23: Generate Parity for a Register Using the TEST Instruction

Figure 3-24: The TEST Instruction Affects the CARRY Flag

7 6 5 4 3 2 1 0

7 6 5 4 3 2 1 0Register sX

Register sY

Literal kk

Bitwise AND

ZERO

If all bit results are zero,

set ZERO flag.

UG129_c3_03_051404

LOAD s0, 05 ; s0 = 00000101

TEST s0, 04 ; mask = 00000100

; CARRY = 1, ZERO = 0

7 6 5 4 3 2 1 0

7 6 5 4 3 2 1 0Register sX

Register sY

Literal kk

CARRY

UG129_c3_04_051404

Mask out unwanted bits.

0=mask bit, 1=include bit

Generate odd parity

(XOR) from bit results.