PicoBlaze 8-bit Embedded Microcontroller www.xilinx.com 111

UG129 (v1.1.2) June 24, 2008

SR[ 0 | 1 | X | A ] sX — Shift Right Register sX

R

The ZERO flag is always 0 after executing the SR1 instruction because register sX is never

zero.

Example

SR0 sX; Shift right. 0 shifts into MSB, LSB shifts into CARRY.

SR1 sX; Shift right. 1 shifts into MSB, LSB shifts into CARRY.

SRX sX; Shift right MSB shifts into MSB, LSB shifts into CARRY.

SRA sX; Shift right CARRY shifts into MSB, LSB shifts into CARRY.

Pseudocode

case (INSTRUCTION)

when “SR0”

MSB Å 0

when “SR1”

MSB Å 1

when “SRX”

MSB Å sX(7)

when “SRA”

MSB Å CARRY

end case

CARRY Å sX[0]

sX Å {MSB, sX[7:1]}

if ( sX = 0 ) then

ZERO Å 1

else

ZERO Å 0

endif

PC Å PC + 1

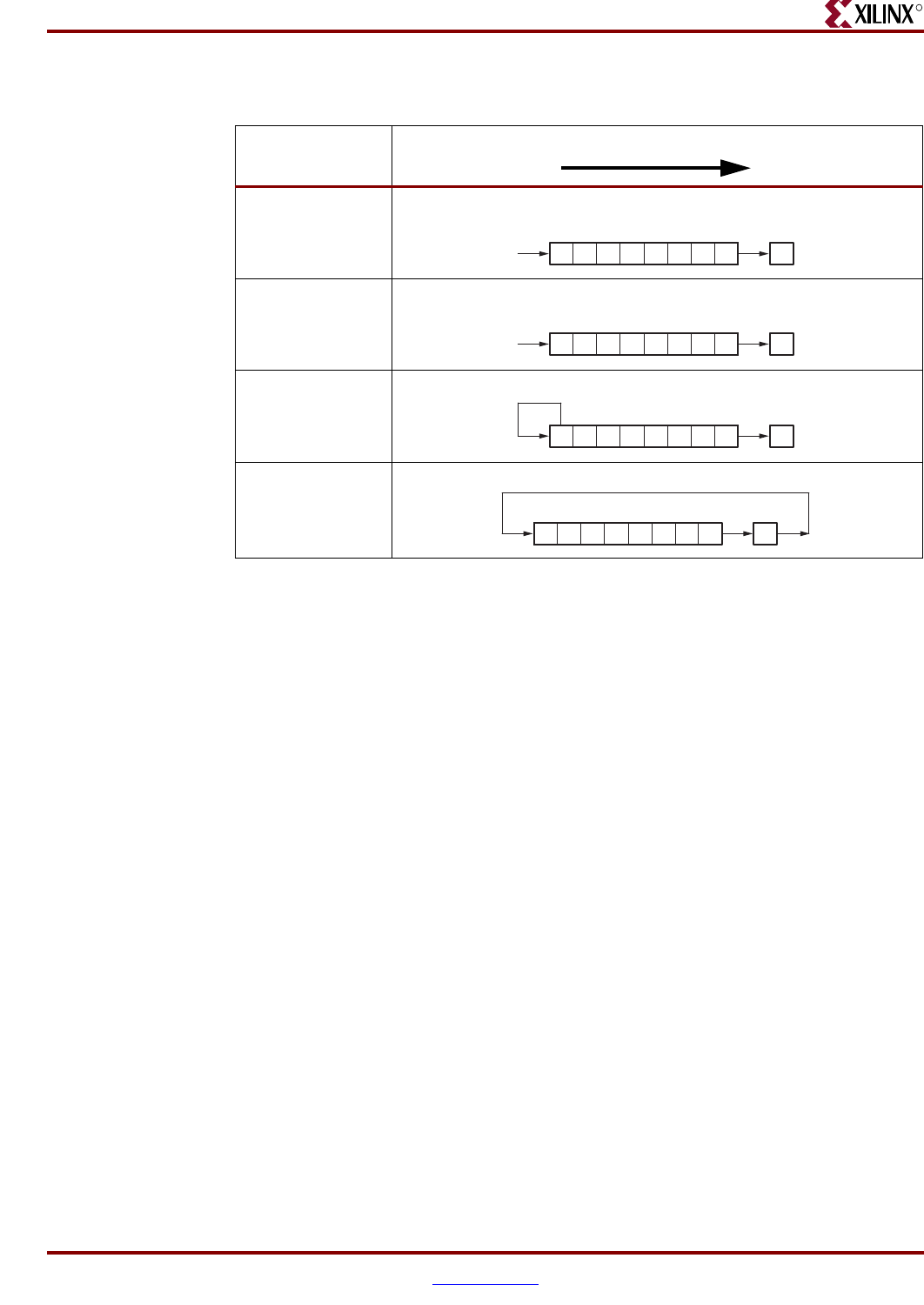

Table C-8: Shift Right Operations

Shift Right

SR0 sX Shift Right with ‘0’ fill.

SR1 sX Shift Right with ‘1’ fill.

SRX sX Shift Right, sign eXtend.

SRA sX Shift Right through All bits, including CARRY.

7 6 5 4 3 2 1 0

Register sX CARRY

‘0’

7 6 5 4 3 2 1 0

CARRYRegister sX

‘1’

7 6 5 4 3 2 1 0

CARRYRegister sX

7 6 5 4 3 2 1 0

CARRYRegister sX