4–28

4.23 Reset

A low on RSINL causes the TCM4300 internal registers to assume their reset values. The power-on reset

circuit also causes internal reset. However, the logic level at RSINL has no effect on reset outputs RSOUTH

and RSOUTL. The effects of resetting the TCM4300 are described in the following paragraphs.

4.23.1 Power-On Reset

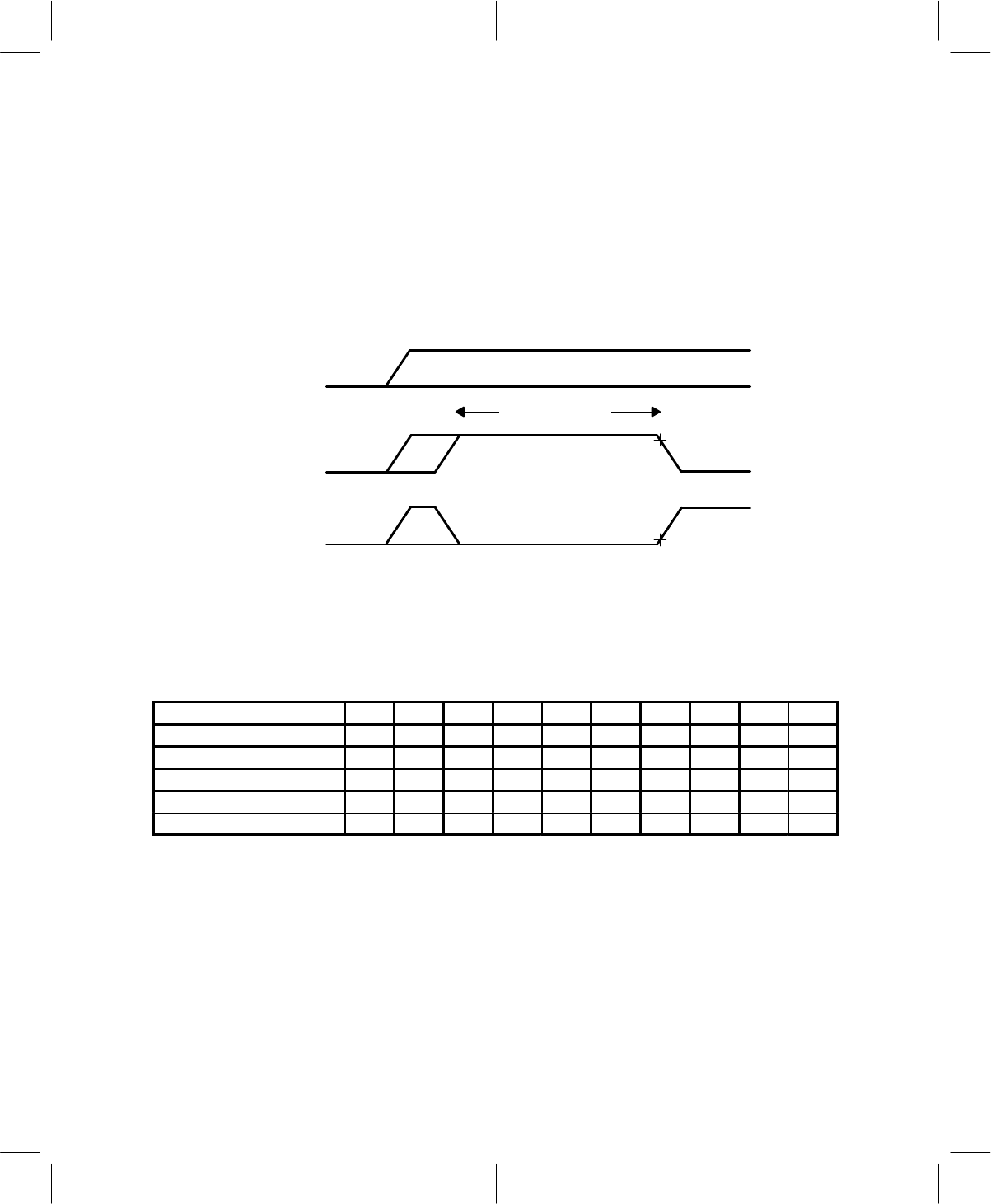

The power-on reset (POR) is digitally implemented and provides a timed POR signal at RSOUTL and

RSOUTH. The POR pulse duration is equal to 388,800 cycles of MCLKIN (10 ms). There are two outputs

to provide a high reset and a low reset in order to accommodate the reset polarity requirements of any

external device. The TCM4300 internal registers are reset when the POR outputs are activated. See

Figure 4–12.

t

w

10 ms Minimum

90%

10%

90%

10%

DV

DD

RSOUTH

RSOUTL

Figure 4–12. Power-On Reset Timing

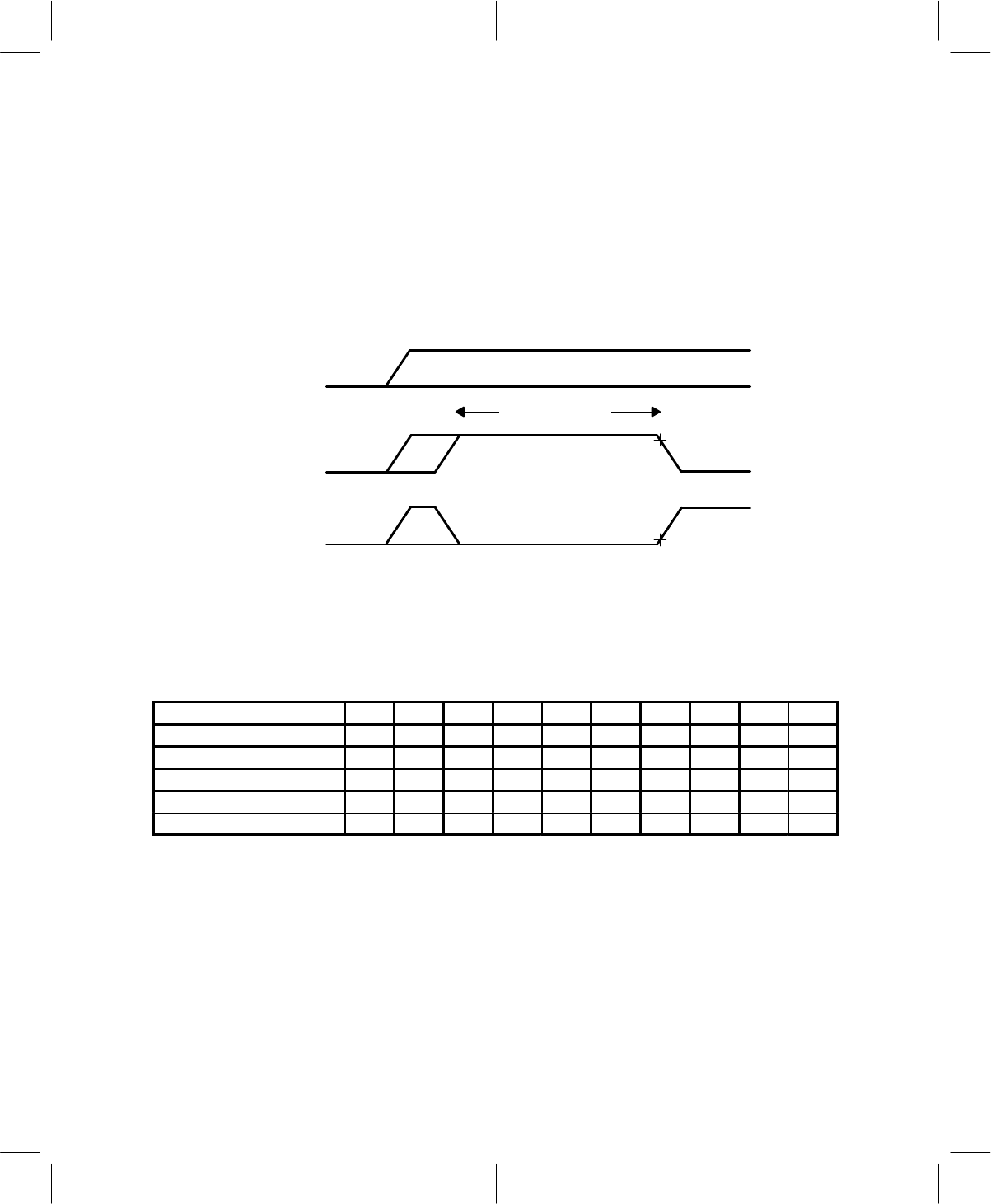

4.23.2 Internal Reset State

After power-on reset, the TCM4300 register bits are initialized to the values shown in Table 4–23. The

synthesizer control terminals SYNCLK, SYNLE0, SYNLE1, SYNLE2, and SYNDTA are high after reset, and

the synthesizer interface circuit is in the stable idle state with no SYNCLK outputs.

Table 4–23. Power-On Reset Register Initialization

REGISTER NAME BIT 9 8 7 6 5 4 3 2 1 0

DIntCtrl 0 1 0 0 0 r r r r r

DStatCtrl 0 0 0 0 0 0 0 0 0 0

MIntCtrl 0 0 0 0 0 0 0 r

MStatCtrl ext ext 1 1 0 0 0 0

MCClock 0 0 0 0 0 0

NOTE 5: r= reserved; ext= bit value from external terminal