4–16

D

E

D

E

D

E

SEL 0

SEL 1

SEL 2

S

R

A

B

A

A = B

A = B

B

A

B ≤ A

B

Clock

Circuit

HIGHVAL

DMUX

LOWVAL

NUMCLKS

5

BIT CNT

[0 . . . 31]

M

U

X

32

32-Bit Data

Register

8

Control

Registers

5

5

5

3

Ready

and

Timing Logic

SYNRDY To MStatCtrl Register

CLKPOL

NUMCLKS

LOWVAL

HIGHVAL

SEL[2:0]

MSB/LSB FIRST

SYNDTA

SYNLE0

SYNLE1

SYNLE2

SYNCLK

µC

Bus

303.75 KHz

MSB/LSB

FIRST

Q

Q

Q

Q

CLKPOL

5

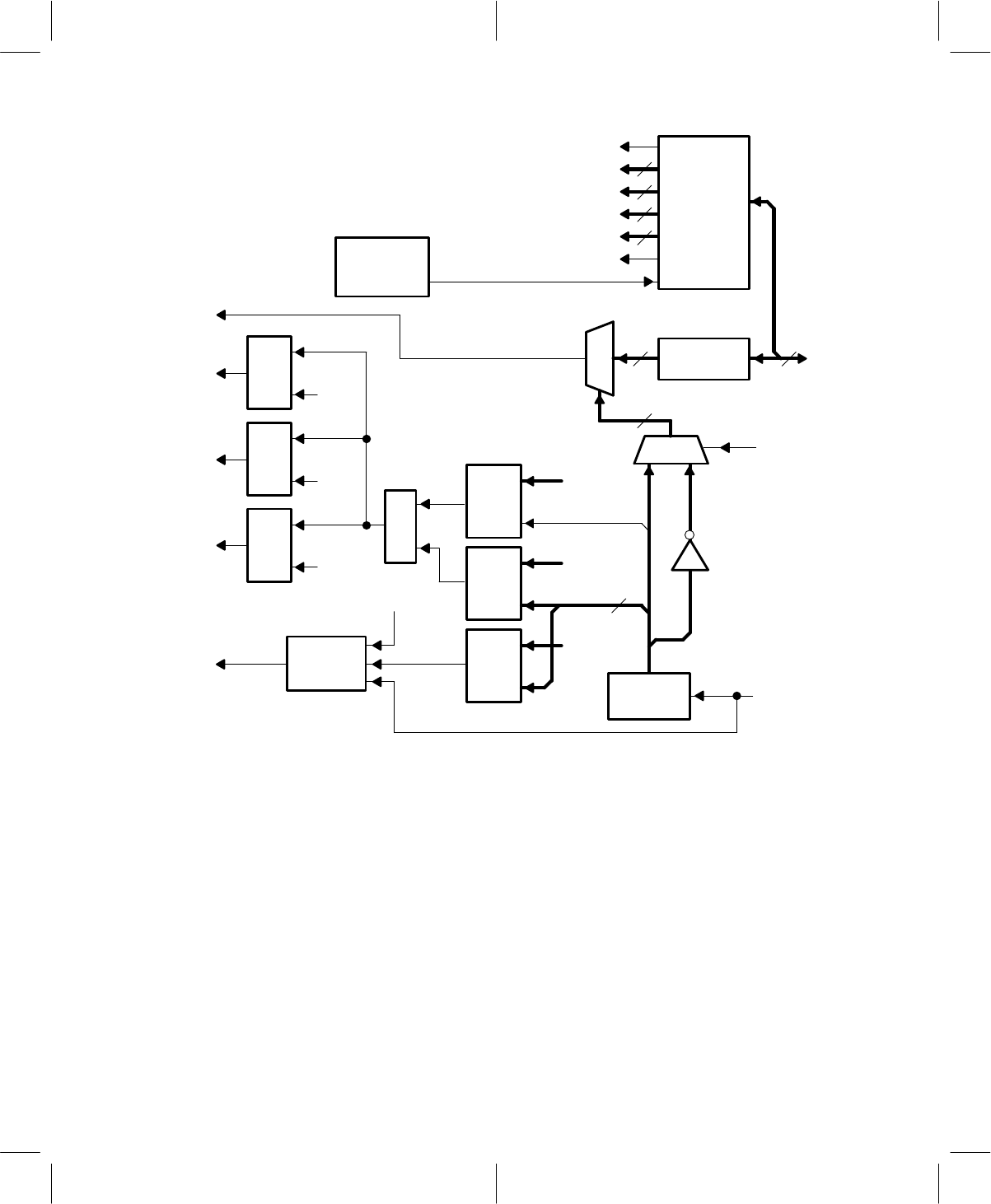

Figure 4–6. Synthesizer Interface Circuit Block Diagram