3–5

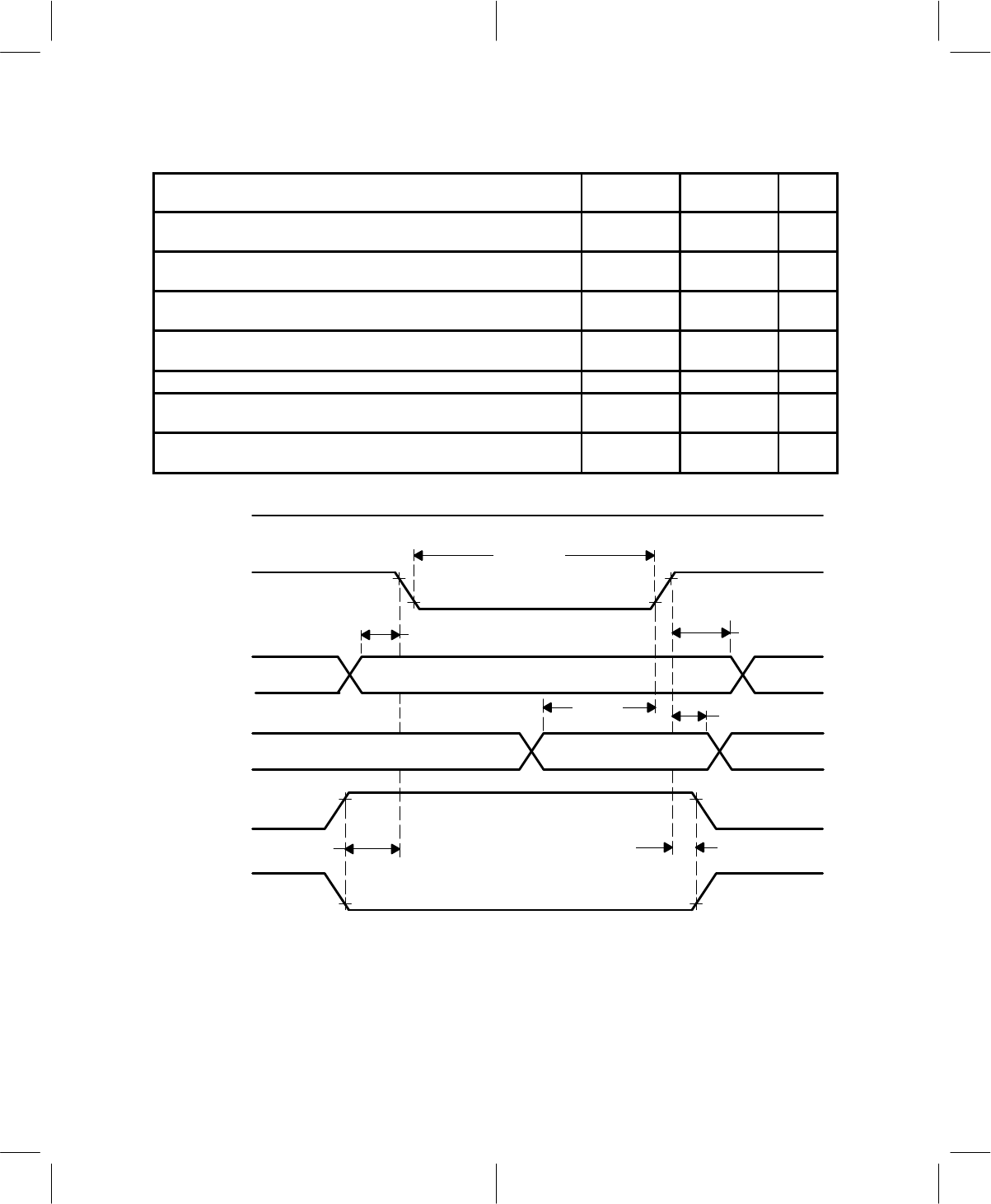

3.5 TCM4300 to Microcontroller Interface Timing Requirements (Intel Write

Cycle) (see Figure 3–5 and Note 3)

PARAMETER

ALTERNATE

SYMBOL

MIN MAX

UNIT

t

su(WA)

Setup time, write address MCA stable before falling edge

of strobe MCRW

TWA

(SU)

0 ns

t

h(WA)

Hold time, write address MCA stable after rising edge of

strobe MCRW

TWA

(HO)

10 ns

t

su(W)

Setup time, write data stable MCD before rising edge of

strobe MCRW

TWD

(SU)

14 ns

t

h(W)

Hold time, write data stable MCD after rising edge of

strobe MCRW

TWD

(HO)

0 ns

t

w(WSTB)

Pulse duration, write strobe pulse width low on MCRW TWR

(STB)

60 ns

t

su(CS)

Setup time, chip select MCCSH and MCCSL stable before

falling edge of strobe MCRW

TCS

(SU)

0 ns

t

h(CS)

Hold time, chip select MCCSH and MCCSL stable before

rising edge of strobe MCRW

TCS

(HO)

0 ns

NOTE 3: Timings are based upon Intel 8C186 (16 MHz).

90%

MCA4–MCA0

MCRW

(see Note A)

MCD7–MCD0

10%

MCDS

t

su(WA)

10%

90%

t

w(WSTB)

t

h(WA)

t

su(W)

t

h(W)

t

su(CS)

t

h(CS)

90%90%

10%10%

MCCSH

MCCSL

NOTE A: Chip selection is defined as both MCCS and MCRW active.

Figure 3–5. Microcontroller Interface Timing Requirements

(Intel Configuration Write Cycle, MTS [1:0] = 00)