4–9

At the same time, the interrupts DWBDINT and MWBDFINT are asserted. The interrupt rate is 800 µs

(8 bits/10 kHz). These interrupts are individually cleared when the WBD register is read by the

corresponding processor. They can also be cleared by their respective processor by writing a 1 to the

corresponding clear WBD bit.

There is one WBD control register. It can be written to by either processor port.

4.8 Wide-band Data Demodulator General Information

The WBDD recovers the transmitter clock from the data stream, which is Manchester encoded, and decodes

the data bits. Consideration at the system level is required to ensure data integrity.

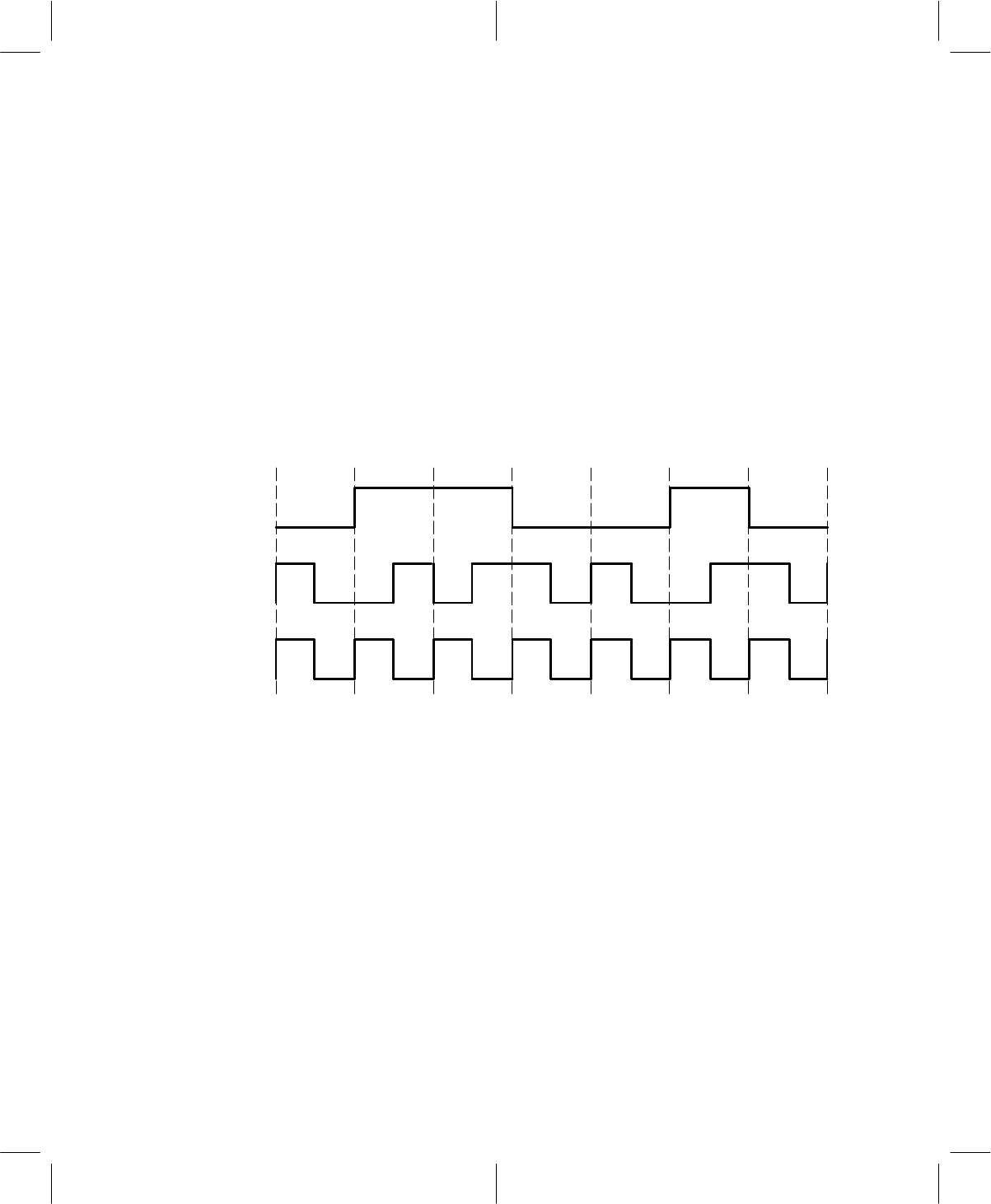

The WBD stream carries with it a 10-kHz clock. The Manchester-coded data format contains a transition

at the middle of every bit-clock period, which aids in clock recovery. The polarity of the transition is

data-dependent. In a typical Manchester-coded WBD stream, a positive voltage for the first half of the data

sequence bit time followed by a negative voltage for the second half of the data sequence bit time represents

the value 0 in the data sequence. Likewise, a negative voltage followed by a transition to a positive voltage

represents the value 1 in the data sequence. This is illustrated in Figure 4–3. The WBD stream can also be

seen as the exclusive-OR of the clock and data sequence. The data sequence is in nonreturn to zero (NRZ)

format.

011 0010

Data

Sequence

WBD

Stream

Recovered Clock

10 kHz

Figure 4–3. WBD Manchester-Coded Data Stream