1–2

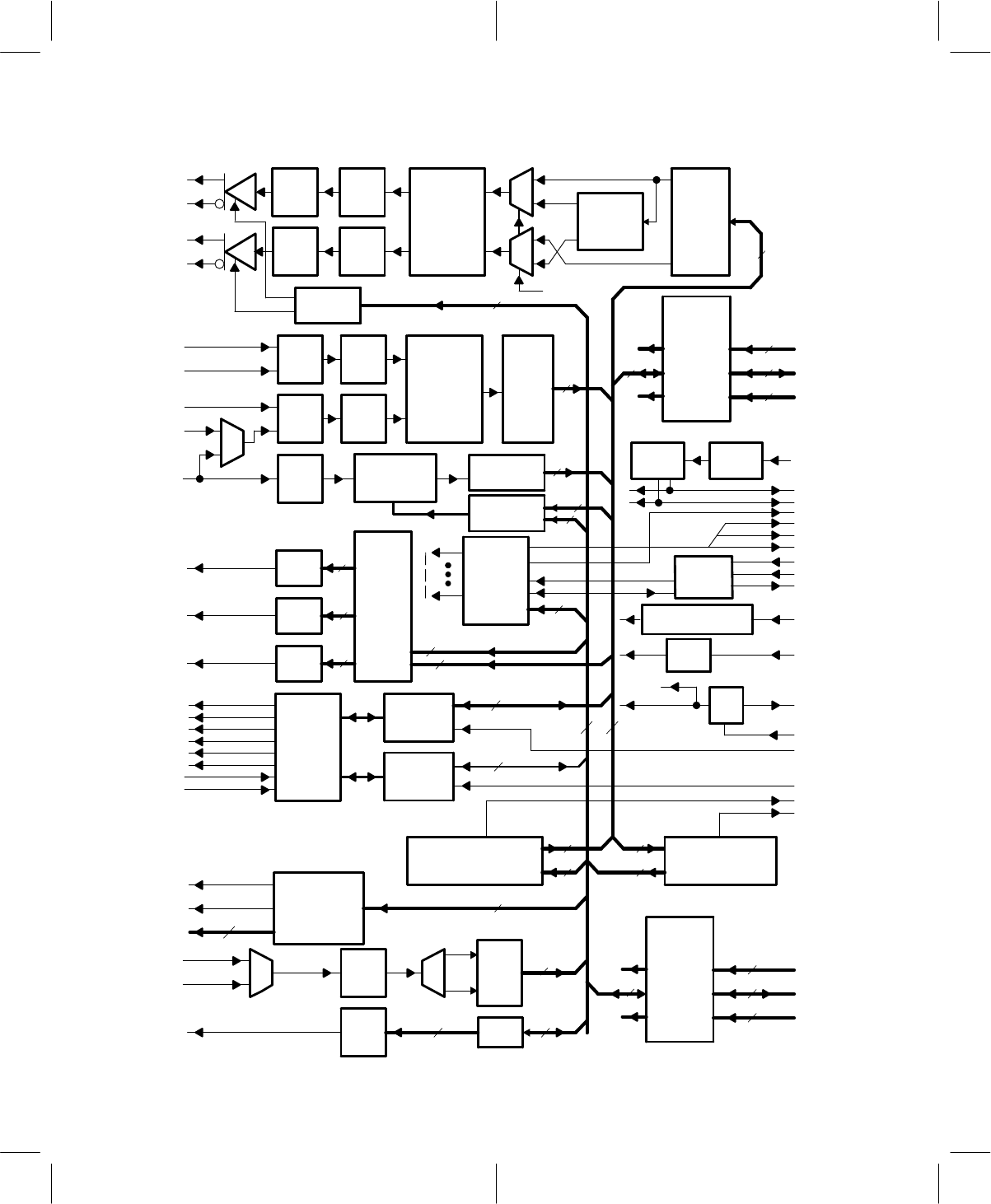

1.2 TCM4300 Functional Block Diagram

TXQP

TXQN

RSSI

BAT

A/D

OUT1

FMRXEN

IQRXEN

TXEN

SCEN

SYNOL

TXONIND

SYNCLK

SYNDTA

SYNLE

[2:0]

LCDCONTR

D/A

TXIP

TXIN

FM

RXQP

RXQN

A/D

RXIP

RXIN

A/D

PWRCONT

AFC

AGC

PAEN

MCCLK

CSCLK

CMCLK

MCLKIN

XTAL

MCLKOUT

CINT

DINT

DWBDINT

MWBDFINT

REFCAP

VHR

Vref

RBIAS

VCM

RSOUTL

RSOUTH

RSINL

DATA

CONTROL

ADDRESS

3

10

4

3

10

8

10

10

8

5

7

8

8

10

8

4

8

4

8

8

8

8

8

8

8

6

0Fh

10h

8

5

I

Q

ModeSel

A

D

D

A

Low-

Pass

Filter

09h(D)

D/A

Low-

Pass

Filter

D/A

Digital Filter

Analog

Mode (LPF)

Digital

Mode (SQRC)

π/4 Shifted

DQPSK

Modulation

TXI (04b)

TX Data

Registers

TXQ (05b)

TX

Offset

Anti-

aliasing

Filter

Digital Filter

Analog

Mode (LPF)

Digital

Mode (SQRC)

Sample

Register

RXI 02h

RXQ 03h

DSP

Interface

Data

Control

Address

Anti-

aliasing

Filter

Low-

Pass

Filter

Wide-band

Data

Demodulator

WBD

Register

00h

WBD

Control

01h

00h

Internal

RESET

Power On

RESET

D/A

D/A

D/A

0Ah(D)

0Bh(D)

AUX

D/As

Control

Registers

Clock

Generation

and

Timing

Adjustment

Logic

38.88MHz

Clock

Oscillator

TX

Common Mode Input

Bias

Control

Ref

Gen

Power

Control

DStatCtrl

Register

0Ch

MStatCtrl

Register

0Eh

Synthesizer

Interface

03h – 09h

Microcontroller

to DSP FIFO

06h

01h

DSP to

Microcontroller

FIFO

06h

01h

RSSI

0Bh

BAT

0Ch

LCD

0Dh

DATA

CONTROL

ADDRESS

6

8

5

8

Micro-

controller

Interface

Data

Control

Address

10

SINT

Internal

Clocks