Rev. 0.5 81

C8051F340/1/2/3/4/5/6/7

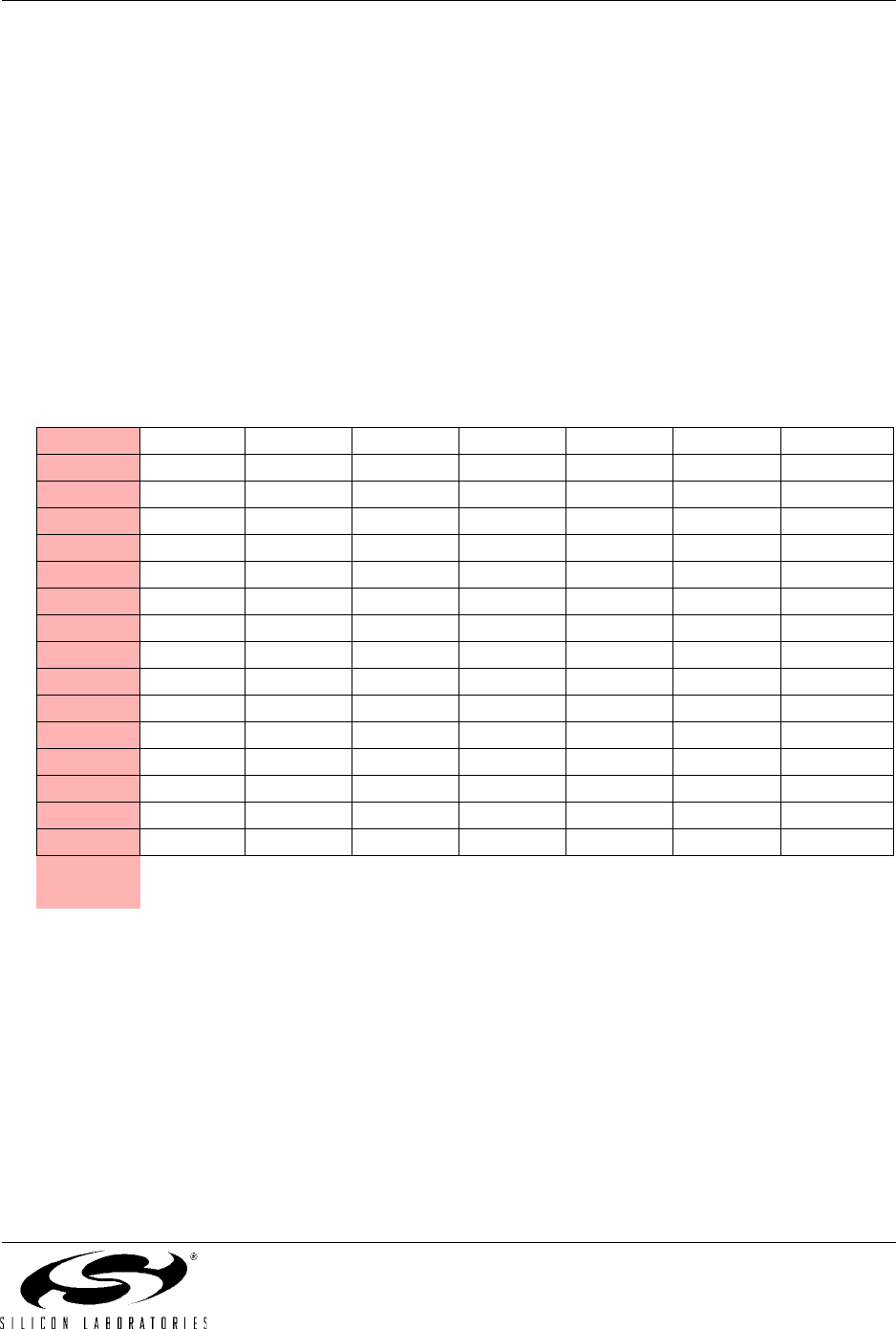

9.2.6. Special Function Registers

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers

(SFRs). The SFRs provide control and data exchange with the CIP-51's resources and peripherals. The

CIP-51 duplicates the SFRs found in a typical 8051 implementation as well as implementing additional

SFRs used to configure and access the sub-systems unique to the MCU. This allows the addition of new

functionality while retaining compatibility with the MCS-51™ instruction set.

Table 9.2 lists the SFRs imple-

mented in the CIP-51 System Controller.

The SFR registers are accessed anytime the direct addressing mode is used to access memory locations

from 0x80 to 0xFF. SFRs with addresses ending in 0x0 or 0x8 (e.g. P0, TCON, SCON0, IE, etc.) are

bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only. Unoccupied

addresses in the SFR space are reserved for future use. Accessing these areas will have an indeterminate

effect and should be avoided. Refer to the corresponding pages of the datasheet, as indicated in

Table 9.3,

for a detailed description of each register.

Table 9.2. Special Function Register (SFR) Memory Map

F8 SPI0CN PCA0L PCA0H PCA0CPL0 PCA0CPH0 PCA0CPL4 PCA0CPH4 VDM0CN

F0

B P0MDIN P1MDIN P2MDIN P3MDIN P4MDIN EIP1 EIP2

E8

ADC0CN PCA0CPL1 PCA0CPH1 PCA0CPL2 PCA0CPH2 PCA0CPL3 PCA0CPH3 RSTSRC

E0

ACC XBR0 XBR1 XBR2 IT01CF SMOD1 EIE1 EIE2

D8

PCA0CN PCA0MD PCA0CPM0 PCA0CPM1 PCA0CPM2 PCA0CPM3 PCA0CPM4 P3SKIP

D0

PSW REF0CN SCON1 SBUF1 P0SKIP P1SKIP P2SKIP USB0XCN

C8

TMR2CN REG0CN TMR2RLL TMR2RLH TMR2L TMR2H - -

C0

SMB0CN SMB0CF SMB0DAT ADC0GTL ADC0GTH ADC0LTL ADC0LTH P4

B8

IP CLKMUL AMX0N AMX0P ADC0CF ADC0L ADC0H -

B0

P3 OSCXCN OSCICN OSCICL SBRLL1 SBRLH1 FLSCL FLKEY

A8

IE CLKSEL EMI0CN - SBCON1 - P4MDOUT PFE0CN

A0

P2 SPI0CFG SPI0CKR SPI0DAT P0MDOUT P1MDOUT P2MDOUT P3MDOUT

98

SCON0 SBUF0 CPT1CN CPT0CN CPT1MD CPT0MD CPT1MX CPT0MX

90

P1 TMR3CN TMR3RLL TMR3RLH TMR3L TMR3H USB0ADR USB0DAT

88

TCON TMOD TL0 TL1 TH0 TH1 CKCON PSCTL

80

P0 SP DPL DPH EMI0TC EMI0CF OSCLCN PCON

0(8) 1(9) 2(A) 3(B) 4(C) 5(D) 6(E) 7(F)

(bit addressable)