Rev. 0.5 149

C8051F340/1/2/3/4/5/6/7

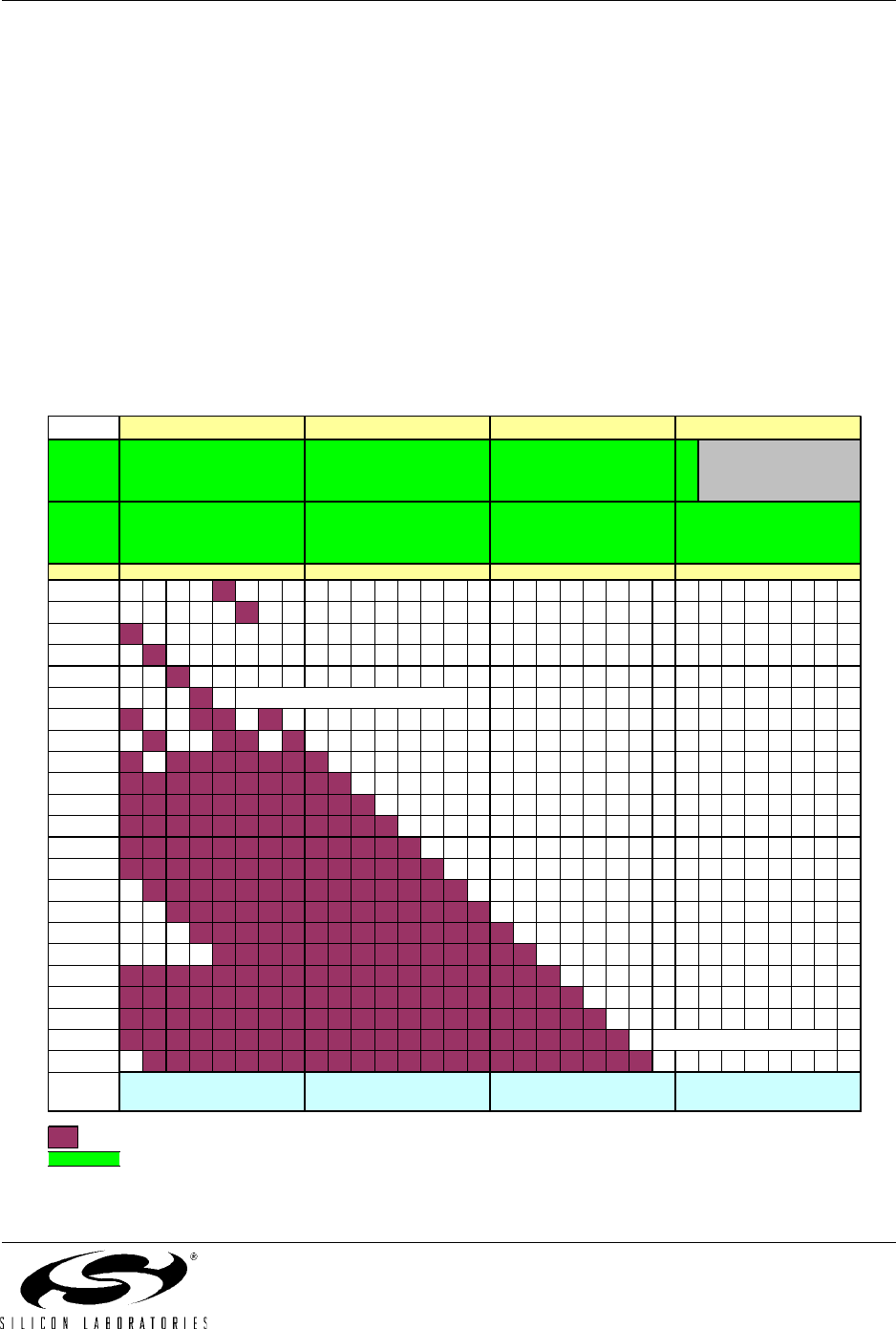

15.1. Priority Crossbar Decoder

The Priority Crossbar Decoder (Figure 15.3) assigns a priority to each I/O function, starting at the top with

UART0. When a digital resource is selected, the least-significant unassigned Port pin is assigned to that

resource (excluding UART0, which is always at pins 4 and 5). If a Port pin is assigned, the Crossbar skips

that pin when assigning the next selected resource. Additionally, the Crossbar will skip Port pins whose

associated bits in the PnSKIP registers are set. The PnSKIP registers allow software to skip Port pins that

are to be used for analog input, dedicated functions, or GPIO.

Important Note on Crossbar Configuration: If a Port pin is claimed by a peripheral without use of the

Crossbar, its corresponding PnSKIP bit should be set. This applies to the VREF signal, external oscillator

pins (XTAL1, XTAL2), the ADC’s external conversion start signal (CNVSTR), EMIF control signals, and any

selected ADC or Comparator inputs. The PnSKIP registers may also be used to skip pins to be used as

GPIO. The Crossbar skips selected pins as if they were already assigned, and moves to the next unas

-

signed pin. Figure 15.3 shows the Crossbar Decoder priority with no Port pins skipped. Figure 15.4 shows

a Crossbar example with pins P0.2 and P0.3 skipped (P0SKIP = 0x0C).

Figure 15.3. Crossbar Priority Decoder with No Pins Skipped

XTAL1

XTAL2

CNVSTR

VREF

XTAL1

XTAL2

ALE

CNVSTR

VREF

/RD

/WR

01234567012345670123456701234567

SCK

MISO

MOSI

NSS*

*NSS is only pinned out in 4-wire SPI mode

CP0

CP0A

CP1

T1

TX1**

**UART1 Only in 48-pin Package

00000000000000000000000000000000

P2SKIP[0:7]

Special Function Signals are not assigned by the Crossbar. When these signals are

enabled, the Crossbar must be manually configured to skip their corresponding port pins.

Port pin potentially available to peripheral

SF Signals

P0SKIP[0:7]

ECI

T0

RX1**

RX0

SDA

SCL

P0

SF Signals

(32-pin

Package)

PIN I/O

TX0

CEX2

CEX0

CEX1

SYSCLK

P3

P3SKIP[0:7]

SF Signals

(48-pin

Package)

P3.1-P3.7 Unavailable on

32-pin Package

P2

CEX3

CEX4

P1SKIP[0:7]

P1

CP1A