C8051F340/1/2/3/4/5/6/7

198 Rev. 0.5

17.4.1. SMBus Configuration Register

The SMBus Configuration register (SMB0CF) is used to enable the SMBus Master and/or Slave modes,

select the SMBus clock source, and select the SMBus timing and timeout options. When the ENSMB bit is

set, the SMBus is enabled for all master and slave events. Slave events may be disabled by setting the

INH bit. With slave events inhibited, the SMBus interface will still monitor the SCL and SDA pins; however,

the interface will NACK all received addresses and will not generate any slave interrupts. When the INH bit

is set, all slave events will be inhibited following the next START (interrupts will continue for the duration of

the current transfer).

The SMBCS1-0 bits select the SMBus clock source, which is used only when operating as a master or

when the Free Timeout detection is enabled. When operating as a master, overflows from the selected

source determine the absolute minimum SCL low and high times as defined in

Equation 17.1. Note that the

selected clock source may be shared by other peripherals so long as the timer is left running at all times.

For example, Timer

1 overflows may generate the SMBus and UART baud rates simultaneously. Timer

configuration is covered in

Section “21. Timers” on page 243.

Equation 17.1. Minimum SCL High and Low Times

The selected clock source should be configured to establish the minimum SCL High and Low times as per

Equation 17.1. When the interface is operating as a master (and SCL is not driven or extended by any

other devices on the bus), the typical SMBus bit rate is approximated by Equation 17.2.

Equation 17.2. Typical SMBus Bit Rate

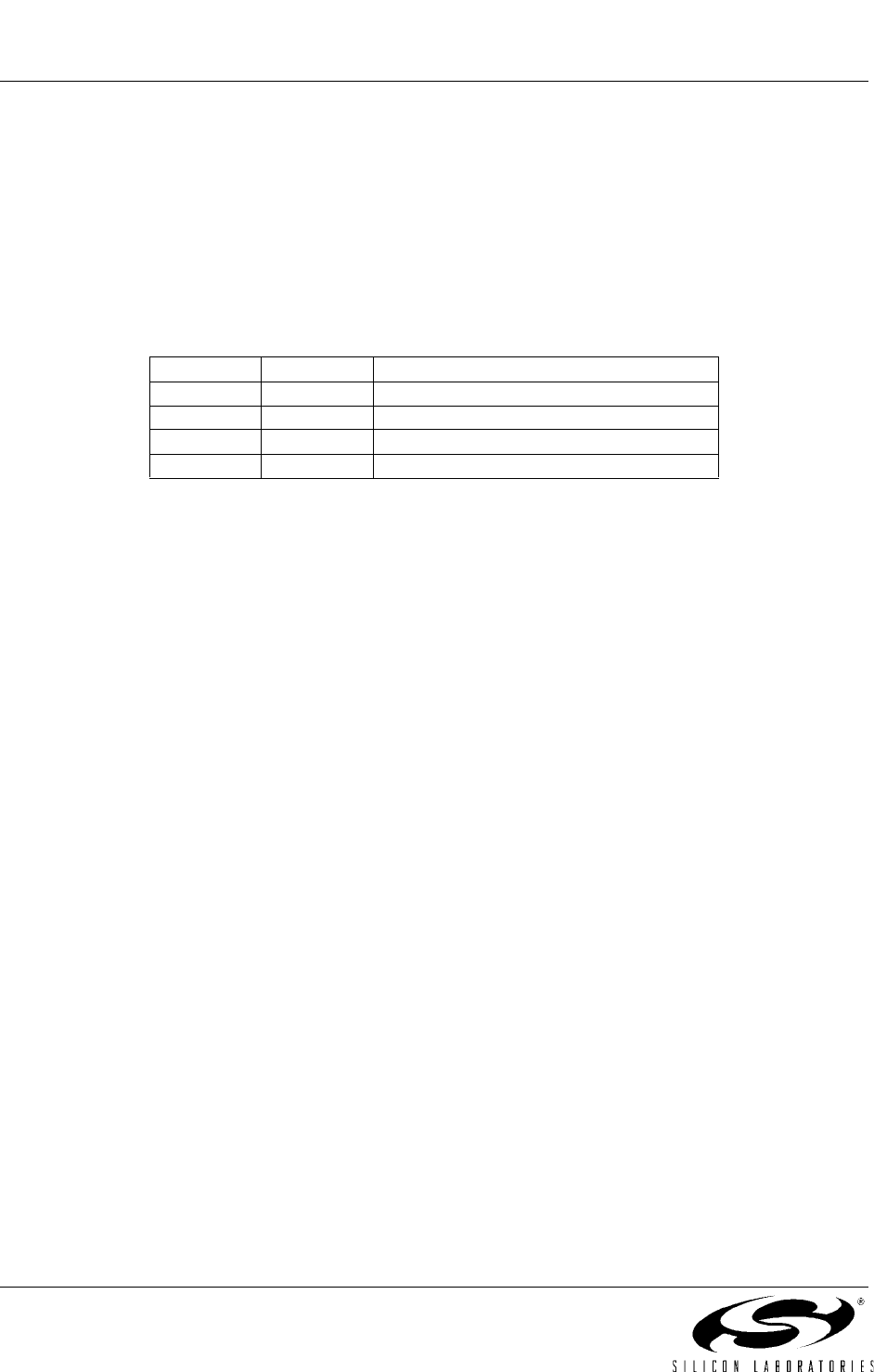

Table 17.1. SMBus Clock Source Selection

SMBCS1 SMBCS0 SMBus Clock Source

0 0 Timer 0 Overflow

0 1 Timer 1 Overflow

1 0 Timer 2 High Byte Overflow

1 1 Timer 2 Low Byte Overflow

T

HighMin

T

LowMin

1

f

ClockSourceOverflow

----------------------------------------------

==

BitRate

f

ClockSourceOverflow

3

----------------------------------------------

=