C8051F340/1/2/3/4/5/6/7

26 Rev. 0.5

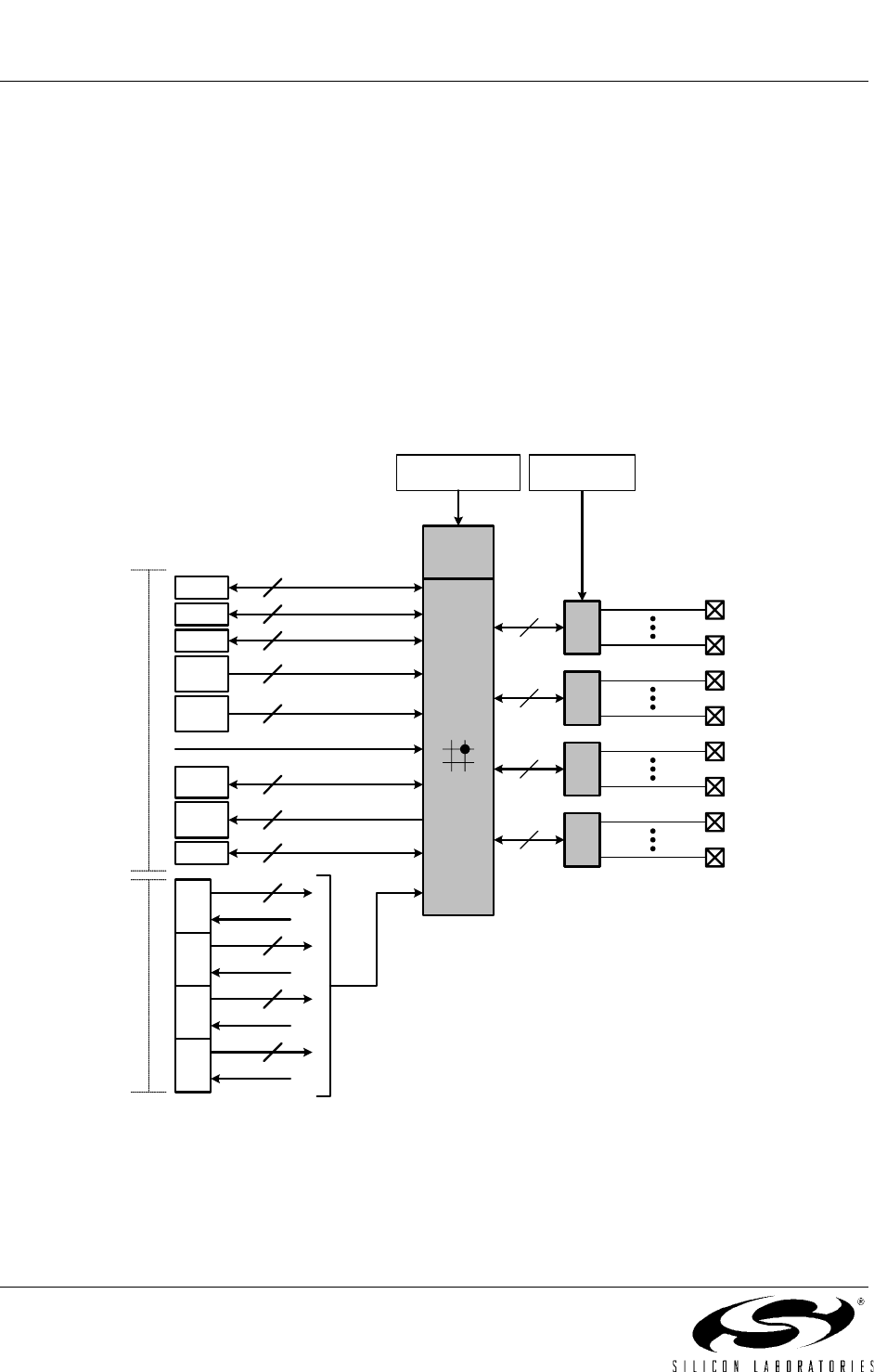

1.6. Programmable Digital I/O and Crossbar

C8051F340/1/4/5 devices include 40 I/O pins (five byte-wide Ports); C8051F342/3/6/7 devices include 25

I/O pins (three byte-wide Ports, and a 1-bit-wide Port). The C8051F340/1/2/3/4/5/6/7 Ports behave like typ

-

ical 8051 Ports with a few enhancements. Each Port pin may be configured as an analog input or a digital

I/O pin. Pins selected as digital I/Os may additionally be configured for push-pull or open-drain output. The

“weak pull-ups” that are fixed on typical 8051 devices may be globally disabled, providing power savings

capabilities.

The Digital Crossbar allows mapping of internal digital system resources to Port I/O pins (See Figure 1.6).

On-chip counter/timers, serial buses, HW interrupts, comparator outputs, and other digital signals in the

controller can be configured to appear on the Port I/O pins specified in the Crossbar Control registers. This

allows the user to select the exact mix of general purpose Port I/O and digital resources needed for the end

application.

Figure 1.6. Digital Crossbar Diagram

XBR0, XBR1, XBR2,

PnSKIP Registers

Digital

Crossbar

Priority

Decoder

2

P0

I/O

Cells

P0.0

P0.7

8

PnMDOUT,

PnMDIN Registers

UART0

(Internal Digital Signals)

Highest

Priority

Lowest

Priority

SYSCLK

2

SMBus

T0, T1

2

6

PCA

CP1

Outputs

2

4

SPI

CP0

Outputs

2

P1

I/O

Cells

P1.0

P1.7

8

P2

I/O

Cells

P2.0

P2.7

8

P3

I/O

Cells

P3.0

8

(Port Latches)

P0

8

8

8

8

P1

P2

P3

*Note: P3.1-P3.7 and UART1 only

available on 48-pin package

UART1*

2

P3.7*

(P0.0-P0.7)

(P1.0-P1.7)

(P2.0-P2.7)

(P3.0-P3.7*)